# 事業戦略ビジョン

実施プロジェクト名:次世代高電力密度産業用電源(サーバ・テレコム・FA等)向けGaNパワーデバイスの開発

実施者名:東芝デバイス&ストレージ株式会社、代表名:代表取締役社長 島田 太郎

# 目次

### 1. 事業戦略·事業計画

- (1) 産業構造変化に対する認識

- (2) 市場のセグメント・ターゲット

- (3) 提供価値・ビジネスモデル

- (4) 経営資源・ポジショニング

- (5) 事業計画の全体像

- (6) 研究開発・設備投資・マーケティング計画

- (7) 資金計画

### 2. 研究開発計画

- (1) 研究開発目標

- (2) 研究開発内容

- (3) 実施スケジュール

- (4) 研究開発体制

- (5) 技術的優位性

### 3. イノベーション推進体制(経営のコミットメントを示すマネジメントシート)

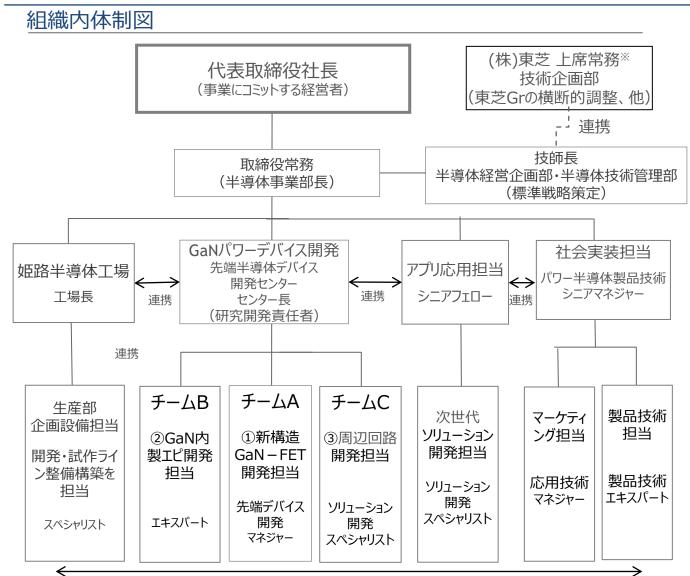

- (1) 組織内の事業推進体制

- (2) マネジメントチェック項目① 経営者等の事業への関与

- (3) マネジメントチェック項目② 経営戦略における事業の位置づけ

- (4) マネジメントチェック項目③ 事業推進体制の確保

### 4. その他

(1) 想定されるリスク要因と対処方針

# 1. 事業戦略・事業計画

### 1. 事業戦略・事業計画/(1)産業構造変化に対する認識

### 社会構造等の変化によりパワーエレクトロニクス産業が急拡大すると予想

#### カーボンニュートラル (CN)を踏まえたマクロトレンド認識

### (社会面)

- 切迫する地球温暖化対策への意識の高まり

- 「望ましい転換」でなく「取り組みが必須」が社会の合意へ、SDGsの策定 (経済面)

- CN取り組みが、ビジネス(事業)へ

- ESG経営への投資規模の拡大

- 設備等の更新投資等はCN仕様が標準へ

- 浸透に伴う規模の拡大で各種コストは低減

### (政策面)

- 設備切替やCN分野の研究開発等を後押しする政策の推進

- 官公庁が模範・リード役を果たす展開

#### (技術面)

- 再生可能エネルギー技術の多様化→送電ロス抑制技術

- 省エネルギー、放熱抑制→インバータ技術の全面浸透、 スイッチング電源の高度化

#### 市場機会:

- ・ 各種規制に適合するための需要の拡大(例 EV化)、

- ・ CN化の全面展開による量的な需要の拡大

- 社会・顧客・国民等に与えるインパクト(パワー半導体):

- 電力変換ロスの低減と機器の軽量化、小型化に貢献

- ・ 駆動と制御の両面で機器の省エネ化実現に貢献

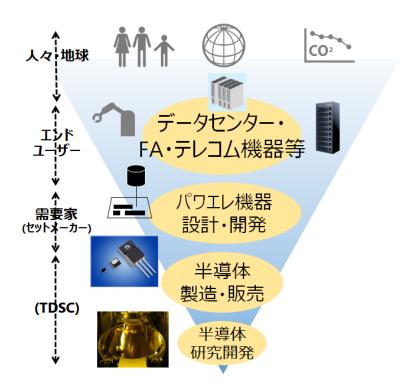

#### カーボンニュートラル社会における産業アーキテクチャ

#### CNに代表されるメガトレンドの課題解決に対しデバイス技術力で貢献

世界の経済力

テクノロジー

- 当該変化に対する経営ビジョン:

- 社会インフラ/情報インフラの進化をリードするキーデバイス/キーコン ポーネンツを提供し続ける

- 環境負荷低減に貢献する製品の創出拡大と、カーボンニュートラルに 向けた取り組みを加速

### 1. 事業戦略・事業計画/(2) 市場のセグメント・ターゲット

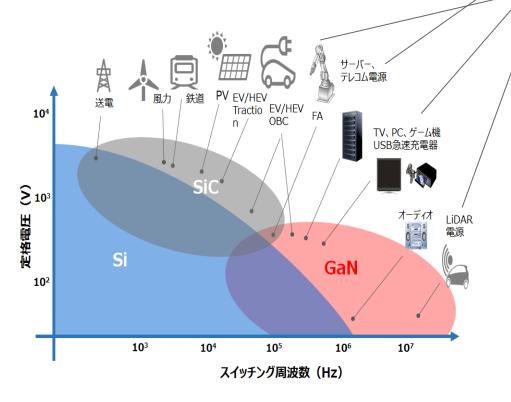

## パワーエレクトロニクス市場のうちGaNデバイス導入効果が大きいスイッチング電源をターゲット

### セグメント分析

GaN: 高周波スイッチングにより、~kWクラスでの

高効率・小型化が求められる機器への応用

#### ターゲットの概要

#### ターゲット市場 (市場規模はGaNパワーデバイスの規模@2030年)

- 産業用電源:サーバー、テレコム、FAなど

- 民生電源:PC、TV、ゲーム機、USB急速充電器

- ・ 車載電源:オンボードチャージャー、車載LiDAR電源

| 需要家 | 主なプレーヤー               | 市場規模     | 課題                                              | 顧客ニーズ                                                                 |

|-----|-----------------------|----------|-------------------------------------------------|-----------------------------------------------------------------------|

| 産業  | 産業用電源メーカー             | • 553億円  | <ul><li>効率</li><li>小型化</li><li>信頼性</li></ul>    | <ul><li>部品点数削減</li><li>低ノイズ</li><li>高放熱パッケージ</li><li>マルチソース</li></ul> |

| 民生  | 電源アダプター等<br>民生用電源メーカー | • 1748億円 | <ul><li>小型・薄型</li><li>軽量化</li><li>コスト</li></ul> | <ul><li>低価格</li><li>集積化</li><li>部品点数削減</li></ul>                      |

| 車載  | 車載電源メーカー              | • 675億円  | <ul><li>効率</li><li>信頼性</li><li>小型・薄型</li></ul>  | <ul><li>IATF16949認証</li><li>高信頼性</li><li>高放熱パッケージ</li></ul>           |

### 各カテゴリィで共通のニーズ

- ・<10kWでの高効率・高電力密度化

- ・機器の小型化

### 1. 事業戦略・事業計画/(3) 提供価値・ビジネスモデル

### 省エネ効果が高い電源用GaNデバイスを提供することで脱炭素社会に貢献

#### 社会・顧客に対する提供価値

- デジタルインフラ機器やEV車の CO2排出量削減に貢献する、 新構造ノーマリーオフ型GaN-FETデバイスを提供する

- ・ GaN素子固有の問題を解決 し、Si同等の使いやすさと低コ ストな標準GaN素子の提供

- 高周波スイッチングが可能な GaN製品群により、電源の高 電力密度化、小型化に貢献

### ビジネスモデルの概要(製品、サービス、価値提供・収益化の方法)と研究開発計画の関係性

- パワエレで標準的な閾値電圧を持つノーマリーオフ型GaN-FETを提供し、業界標準に

- GaN-FETに加え、制御回路/周辺回路も含む製品ラインアップを提供。基板設計のしやすさを訴求

- 顧客設計のための技術情報や評価ボード提供などの技術サポート

- Siビジネスでの強固な顧客基盤によりグローバルな販売網・技術サポート体制

### 1. 事業戦略・事業計画/(3) 提供価値・ビジネスモデル(標準化の取組等)

## 市場導入(事業化)しシェアを獲得するために、ルール形成(標準化等)を検討・実施

標準化を活用した事業化戦略(標準化戦略)の取組方針・考え方

#### ターゲット市場の特徴

#### <産業用電源レイヤ>

- ・電力変換効率を追求

- ・Siデバイス応用による性能飽和の 顕在化と化合物半導体への期待大

- ・コストと共にマルチソースが重要

- <GaN半導体デバイスレイヤ>

- ・パワエレ標準となるデバイスの不在

#### 自社の強み

- ・Siビジネスでの強固な顧客基盤

- ・グループ内にGaN材料・デバイス 基礎研究の蓄積・実績がある (基本特許取得、学術発表)

- ・主要プロセス技術の蓄積と活用

#### 戦略

- ・知財獲得のクローズ戦略を優先

- ・Siデバイスで培われたパワエレ標準に準拠した、GaNデバイスの早期開発・ 市場投入と、顧客基盤を活かした有力顧客との連携によるデファクト標準化

#### 国内外の動向・自社の取組状況

#### (国内外の標準化や規制の動向)

- アプリケーションレイヤ:電力変換効率規格

- 半導体レイヤ: JEITA、JEDEC、及びIECでGaN素子に関わる規格策定が進んでいる

(これまでの自社による標準化、知財、規制対応等に関する取組)

- 基本特許の取得

- 製品仕様(パッケージ外形、性能)の公開

- スイッチング電源応用例(リファレンスモデル)の公開

- 国内外のコンソーシアム参画による情報収集

- JEITA信頼性規格の策定を主導

- 業界団体各種委員会への参加

本事業期間におけるオープン戦略(標準化等)またはクローズ戦略(知財等)の具体的な取組内容(※推進体制については、3.(1)組織内の事業推進体制に記載)

#### クローズ戦略(知財等)

- 特許取得

- ノウハウは非開示

### オープン戦略(標準化等)

- 仕様等の公開

- 顧客レイアと連携し、デファクト化を推進

- 学会、展示会等の活用(デバイス、および電源応用)

### 1. 事業戦略・事業計画/(4)経営資源・ポジショニング

## 実績あるパワー半導体の強みを活かして、環境負荷低減に貢献

### 自社の強み、弱み(経営資源)

#### ターゲットに対する提供価値

- パワエレ業界標準閾値の高効率・MHz級スイッチング 可能なGaNパワーデバイス、及びドライブ回路により、

- 顧客システムの高効率化・電力損失低減

- パワエレ機器の小型・薄型・軽量化と効率の両立

広くパワエレ機器の電力削減に貢献し、カーボンニュートラル社会の実現に貢献

#### 自社の強み

- パワー半導体技術の実績と人材

- エピタキシャル成長の保有技術

- グローバルで幅広い顧客基盤

#### 自社の弱み及び対応

- GaNの製品化では後発も、パワエレの標準閾値電圧のノーマリーオフ型GaN-FETの製品化で巻返しを図る

- グループ内にユーザ不在も、社外パートナーと連携していく

#### 他社に対する比較優位性 顧客基盤 サプライチェーン その他経営資源 技術 【現在】 白汁 • (株) 東芝 研究開 • ノーマリオンGaN+しきい Siで構築した幅広 エピウェハ外部調達 発センター研究者 い顧客基盤 值補下回路 自計グループにエピ装 •6インチ エピウェハを調達 置メーカ(NFT\*) 【将来】 東芝グループ部門横 • ノーマリオフ型新構造 エピ内製化 Si顧客基盤を 断による競争優付な GaN-FETでSiデバイスと 有効活用 自社グループ装置 開発体制の構築と技 同等の使い易さを追求 新規顧客の獲得 メーカとの共同開発 術者育成 • 内製・8インチ化によるコス 卜低減、高品質化 Si、化合物の ノーマリオフGaN 6インチ内製 豊富なアプリケーショ 顧客基盤あり 8インチ化検討中 ンエンジニア (GIT型) ゲート誤オン耐性」 M&Aにより技術・ 専用回路要 顧客基盤強化 GaNパワーデバイス ノーマリオンGaN+Nch • GaN顧客のみ 6インチ内製 競合 T社 製品化のパイオニア LVMOS逆回復特性↓ スルーレート制御不可

### 1. 事業戦略・事業計画/(5) 事業計画の全体像

# 7年間の研究開発の後、150W/in3電源向けGaNデバイスを29年頃の事業化、GaNデバイス事業全体の投資回収は32年頃を想定

### 投資計画

- ✓ 本事業終了後も約1年程度、研究開発を継続し、ノーマリオフ型GaNパワーデバイスについて29年度頃の事業化を目指す。

- ✓ 産業用電源市場での販売を図り、32年度頃に投資回収できる見込み。

|                       |             |      | 4           | 研究開発  |             |                |                   | 事業化      | ľĽ   |        | 投資回      | 叫又   |

|-----------------------|-------------|------|-------------|-------|-------------|----------------|-------------------|----------|------|--------|----------|------|

|                       |             |      |             |       | · 1         |                |                   | <b>V</b> |      | T      | <b>V</b> |      |

|                       | 22年度        | 23年度 | 24年度        | 25年度  | 26年度        | 27年度           | 28年度              | 29年度     | 30年度 | 31年度   | 32年度     | 33年度 |

| 売上高                   |             |      |             |       |             |                |                   |          |      | 約680億円 |          |      |

| 研究開発費                 |             |      | 約95億円       | (本事業の | 支援期間)       |                |                   | 約8億円     |      |        |          |      |

| 取組の段階                 | 研究開発の開<br>始 |      | 研究<br>サンプル① |       | 研究<br>サンプル② | ドライブIC<br>サンプル | 電流センシング研<br>究サンプル |          |      |        |          |      |

| CO₂削減効果<br>(万t – CO2) | 0           | 0    | 0           | 0     | 0           | (              | ) 0               | 0        | 329  | 398    | 516      | 588  |

### 1. 事業戦略・事業計画/(6)研究開発・設備投資・マーケティング計画

### 研究開発段階から将来の社会実装(設備投資・マーケティング)を見据えた計画を推進

|      |                                                                                                                                                                        |                                                                             | マーケティング                                                                                                                |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 取組方針 | <ul> <li>本プロジェクトで得られた知見は、速やかに知財化を検討する</li> <li>技術が確立しているSi搭載電源を基準として、GaNデバイスの有効性を検証する</li> <li>連携企業には、初期段階から参画頂き、シュミレーションも活用してGaNデバイスの有用性を検証、またニーズを把握しながら開発</li> </ul> | <ul> <li>研究試作ラインを構築</li> <li>エピ開発・生産拠点、及び大口径化合物<br/>専用生産ラインを整備予定</li> </ul> | <ul> <li>既存Si販売顧客、チャネルを活かした拡販推進</li> <li>製品リリースにあわせた顧客サポート体制やWebコンテンツを拡充</li> <li>顧客VoC入手により製品改善、試作へフィードバック</li> </ul> |

| 進捗状況 | <ul><li>知財実績(GI外含む出願ベース、海外含め): 約60件出願</li><li>GaNデバイスの有用性実証に向け、連携会</li></ul>                                                                                           | <ul><li>研究試作ライン構築に向け準備中</li><li>エピ開発向けの装置を導入</li></ul>                      | • GaNデバイスの電源応用に関して、顧客レイヤ<br>の検討促進のための諸活動を推進中                                                                           |

### 国際競争 上の 優位性

• パワエレ標準の閾値と高周波スイッチングに 適した特性を実現可能な独自技術を保有 している

社との協議を実施

- 開発初期からユーザ企業に参画頂き、ニーズに合致した製品を他社に先駆けて上市可能

- 東芝デバイス&ストレージ(株)グループ内 に半導体装置メーカーのニューフレアテクノロ ジー(株)を保有しており、垂直統合型の デバイス開発が可能

- GaNエピタキシャル工程を内製化し、品質及びコスト競争力向上を目指す

• 国内パートナーと協業し、開発、製品化を加速

## 参考資料:メガトレンドとGaNパワーデバイス

## 高周波スイッチングにより機器の高効率・小型・軽量化に貢献

## エネルギー

カーボンニュートラル 実現に向けた電力の 高効率利用

### 高効率·軽量化···走行距離延伸

- ・車載 (OBC/コンバータ/インバーター)

- ・電動航空機(モーターインバーター) など

### 高効率·小型化···大容量·高電力密度化

- サーバー/テレコム電源

- ・モバイルバッテリィ など

## モビリティ

電動化による脱炭素の実現

## 情報通信

データセンター増設 と5G/6G通信サー ビス拡大 参考資料:社会実装を見据えた取り組み (GaN全体)

ユーザー要求を満たすユーザーフレンドリーな製品による市場参入と拡大

1 高性能・高品質・低コストGaNパワーの創出

2 システム性能とコストを考慮した製品ラインナップ の拡充

3 顧客技術サポートの充実

### 1. 事業戦略・事業計画/(7)資金計画

## 国の支援に加えて、201億円規模の自己負担を予定

単位:億円

|               | 2022<br>年度 | 2023<br>年度 | 2024<br>年度 | 2025<br>年度 | 2026<br>年度 | 2027<br>年度 | 2028<br>年度 | 2029<br>年度 | 2030<br>年度      | 2031<br><sub>年度</sub> | 2032<br>年度       | 2033<br><sup>年度</sup> |

|---------------|------------|------------|------------|------------|------------|------------|------------|------------|-----------------|-----------------------|------------------|-----------------------|

| 事業全体の<br>資金需要 |            |            | ή          | 约223億円     |            |            |            |            |                 |                       |                  |                       |

| うち研究開発投資      |            |            |            | 約95億円      |            |            |            | き高効率の      | SaNデバイス         | 技術の確立                 | 了させた後、<br>に向け、自己 | 2負担                   |

| 国費負担※<br>(補助) |            |            |            | 約22億円      |            |            |            |            | 的な研究開<br>を実施する予 |                       | 量産ライン棒           | 5築等の                  |

| 自己負担          |            |            | ý          | 的201億円     |            |            |            |            |                 |                       |                  |                       |

※2029年度以降のインセンティブを含む国費負担の総額

# 2. 研究開発計画

### 2. 研究開発計画/(1)-1 研究開発目標

## 「電源効率98%、電力密度150W/in<sup>3</sup>」を達成するために必要なGaN素子特性のKPI

### 研究開発項目

1.ノーマリオフ型新構造GaN-FETの開発

### アウトプット目標

効率98%(損失50%減)、電力密度150W/in<sup>3</sup>を満たす電源向けGaNパワー素子

### 研究開発内容

デバイス構造設計

#### **KPI**

(a) Vth、(b) 移動度、(c) 出力電 荷量、(d) 耐圧の各項目につい て、KPI設定の考え方を満たすデ バイス構造設計を決定する。

### KPI設定の考え方

- (a) スイッチング時のノイズによる誤作動防止に十分な値であること cf. Si系パワーMOSFETのVth = 3 V

- (b) 高速スイッチング可能、且つ、導通損失低減に寄与

- (c) SW損失低減に寄与

- (d) 定格電圧650Vに対して余裕がある耐圧

2 要素プロセス開発 ・MOS構造形成

- (a) Vth、(b) 移動度は①の設計を 実現するMOS形成プロセスであること。(c) ΔVth (BTI試験)、(d) TZDB は、パワー素子の一般的な値を実現。

- (a)(b) Vthやµはデバイス構造、チャネル層やゲートの物理パラ メータなどに依存

- (c)(d) 構造形成部のダメージや、ゲート/チャネル部のラフネス等は、素子の電気的安定性やゲート絶縁膜の破壊電圧に影響

- 3 プロセスインテグレーション

- (a) チャネル抵抗・出力容量積は、 KPI設定の考え方を満足すること。 (b) 研究開発内容①②記載のKPIを 実現し、且つ(a)を同時に満足するプロセスフローを確立する

- ①導通損失、スイッチング損失、デッドタイム時間等のユーザリク アイメントを満たす指標として設定

- ②研究開発内容①②に記載の通り

- ③実用化に向けて、特性と信頼性を単一素子レベルで満たすことが必要

### 2. 研究開発計画/(1)-2 研究開発目標

## コストが「Siと同等」を達成するための鍵となる、GaNエピタキシャルプロセスのKPI

#### アウトプット目標 研究開発項目 2.高品質・低コストエピタキシャル成 コストが「Siと同等」を満たすSi基板上へのGaNエピタキシャルプロセス 長技術の基礎開発 研究開発内容 KPI設定の考え方 **KPI** (a) 表面欠陥密度、(b) 転位密度は、 低欠陥化 歩留、および信頼性向上を実現するために必要な指 KPI設定の考え方に基づき、現状のファク 標として設定 ター以下を実現する (a) 耐圧やリーク歩留向上に寄与 (b) 閾値電圧やオン抵抗変動抑制に寄与 2 大口径化 (a) 反り、(b) クラックの長さは、デバイス製 (a) デバイスプロセス不良の抑制に寄与 造工程に不具合が生じない範囲に抑制す (b) デバイスプロセス時のウェハの割れ抑制、ウェハの 有効面積拡大による低コスト化に寄与 る。 ただし、研究開発項目1の指標を満たす膜厚であ ること。 (a) 成長速度の高速化やプロセスシーケンスを改善 (a) 結晶成長プロセス時間は、現状に対し 3 スループット向上 ファクターで削減する し、結晶成長時間を短縮

### 2. 研究開発計画/(1)-3 研究開発目標

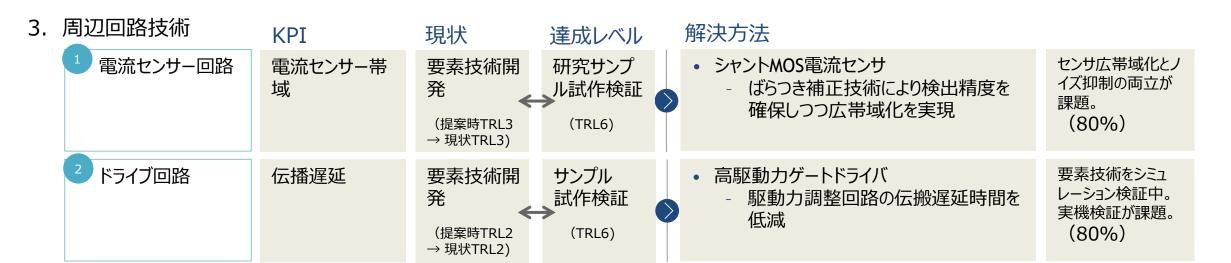

## 電源の電力密度 150W/in³ に向けたGaNパワーデバイス開発、及び全体検証のKPI

#### 研究開発項目

3. 周辺回路技術

#### 研究開発内容

1 電流センサー回路

2 ドライブ回路

4. PoCの試作と評価

### 研究開発内容

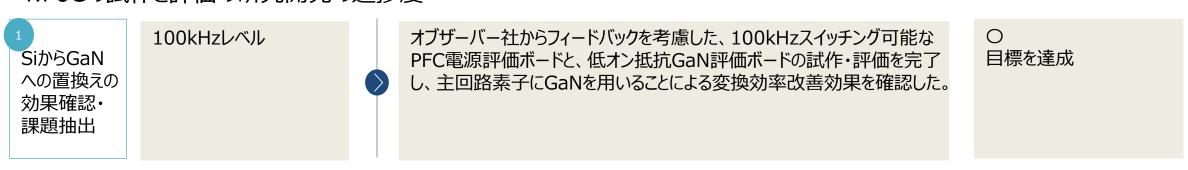

- 1 SiからGaNへの置換え の効果確認・課題抽出 (既存GaN評価ボード)

- ② 高周波スイッチング化の 効果確認・課題抽出

- 3 高電力密度化の効果 確認・課題抽出

### アウトプット目標

電源の電力密度150W/in3を満たす電源向けGaNパワーデバイス

→ 高周波スイッチング電源の実用化に必要となるGaNパワー素子周辺回路を開発

#### **KPI**

電流センサー帯域は、現状に対し て5倍以上を実現

伝播遅延は、KPI設定の考え方に 基づく伝番遅延を実現

### KPI設定の考え方

高周波スイッチング電源のピーク電流制御のための電流検出に十分な電流センサーを目指す。

高周波スイッチング電源に対応する制御性と保護性能確保に十分なターンオン及びターンオフ伝播遅延を目指す。

### アウトプット目標

電力密度150W/in³、コストSi同等満たす電源実現に向けた試作・評価

→ 高周波スイッチング電源のPoCを構想・企画すると共にデバイス側にFB。最終的に試作・評価を実施

#### KPI

スイッチング周波数:現状と同等レベル

スイッチング周波数:数倍

スイッチング周波数:桁倍

### KPI設定の考え方

SiとGaNの素子パラメータの違いによる電源回路特性への影響を評価頂く(理論計算・シミュレーション・実測など)

スイッチング周波数を変えた場合の、受動部品も含めた電力密度・損失・コストへの影響を検討するための基礎評価

高周波スイッチング電源の電力密度・損失・コストを検証するためのPoCを構想・企画・試作・評価

## 2. 研究開発計画/(2)-1 研究開発内容(全体像)

## ノーマリオフ型新構造GaN-FETの開発KPIの目標達成に必要な解決方法

|                        | KPI                                                                       | 現状                              | 達成レベル                       |   | 解決方法                                                                                                 | 実現可能性<br>(成功確率)                                   |

|------------------------|---------------------------------------------------------------------------|---------------------------------|-----------------------------|---|------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 1 デバイス構造設計             | (a) Vth<br>(b) 移動度<br>(c) 出力電荷量<br>(d) 耐圧                                 | 要素技術開発<br>《提案時TRL4<br>→現状TRL4)  | サンプル<br>試作検証<br>(TRL6)      | > | (a)(b) 要素プロセス技術の量産ラインへの適用<br>(c)(d)・MOS型デバイスにけるFP設計技術開発<br>・高電界下のゲート-ドレイン間における<br>空乏層制御による電界分布制御技術開発 | コンセプト確認済、<br>デバイスとしての<br>検証を進める<br>(65%)          |

| 2 要素プロセス開発<br>・MOS構造形成 | (a) Vth<br>(b) 移動度<br>(c) ΔVth (BTI試験)<br>(d) TZDB                        | 要素技術開発<br>(提案時TRL4<br>→現状TRL4)  | サンプルを試<br>作して検証<br>・ (TRL6) | > | (a) MOS構造最適化によるしきい値制御技術開発<br>(b) チャネル領域の高品質化技術開発<br>(c)(d) ゲート絶縁膜の高品質化技術開発                           | コンセプト確認済、<br>要素技術の深耕<br>とデバイスへの展<br>開を図る<br>(85%) |

| 3 プロセスインテグレー<br>ション    | (a)チャネル抵抗・出<br>力容量積<br>(b) 研究開発校項目<br>①②記載のKPI<br>(c) (a)(b)を同時に<br>満たすこと | 要素技術開発<br>(提案時TRL4)<br>→現状TRL4) | サンプルを試<br>作して検証<br>(TRL6)   |   | (a)(b)(c)・要素プロセス技術の量産ラインへの適用・MOSゲートプロセスとFP構造プロセスのプロセスインテグレーション技術開発                                   | コンセプト確認済、<br>デバイスとしての<br>検証を進める<br>(60%)          |

### 2. 研究開発計画/(2)-2 研究開発内容(全体像)

## GaNエピタキシャルプロセスKPIの目標達成に必要な解決方法

|            | KPI                    | 現状                                     | 達成レベル                      | 解決方法                                                                               | 実現可能性<br>(成功確率)                        |

|------------|------------------------|----------------------------------------|----------------------------|------------------------------------------------------------------------------------|----------------------------------------|

| 1 低欠陥化     | (a) 表面欠陥密度<br>(b) 転位密度 | 技術コンセプ<br>トを確認<br>(提案時TRL3→<br>現状TRL4) | パイロットライ<br>ンでの検証<br>(TRL6) | (a) 表面欠陥発生メカニズム解明と抑制技術確立<br>(b) 転位生成・消滅メカニズムの解明<br>反りとの両立が可能な転位制御層の開発              | コンセプト確認済<br>み、大口径化と<br>の両立が課題<br>(65%) |

| 2 大口径化     | (a) 反り<br>(b) クラック     | 要素技術開発<br>(提案時TRL4<br>→現状TRL4)         | パイロットライ<br>ンでの検証<br>(TRL6) | (a) 応力バランスを適正化する層構造設計とエピタキ<br>シャル成長技術の開発<br>反り・欠陥を抑制する結晶成長基板の検討<br>(b) 高品質界面形成技術開発 | 構造設計と実現<br>に必要な要素技<br>術を開発中<br>(85%)   |

| 3 スループット向上 | (a) 結晶成長プロ<br>セス時間削減   | 要素技術開発<br>(提案時TRL3<br>→現状TRL4)         | パイロットライ<br>ンでの検証<br>(TRL6) | (a) 高品質エピタキシャル結晶の高速成長技術開発                                                          | 要素技術を開発<br>中、大口径化と<br>の両立が課題<br>(75%)  |

サイローテムとルル

### 2. 研究開発計画/(2)-3 研究開発内容(全体像)

## 各KPIの目標達成に必要な解決方法を提案

### 4. PoCの試作と評価

- 1 SiからGaNへの置換えの効果確認・課題抽出 (既存GaN評価ボード)

- 2 高周波スイッチング化の 効果確認・課題抽出

- 3 高電力密度化の効果 確認・課題抽出

「次世代高電力密度産業用電源(サーバ・テレコム・FA等)向けGaNパワーデバイスの開発」という開発テーマにおいて、本研究項目は、

- 電源応用向けのGaNデバイスの仕様策定へのFB

- 研究開発したGaNデバイスによりSiでは実現し得ない電源が実現できることの検証を主目的とするもの。

電源開発そのものが主目的ではなく、オブザーバー企業との連携により実施。

### 2. 研究開発計画/(2) 研究開発内容(これまでの取組)

## ノーマリオフ型新構造GaN-FETの研究開発の進捗度

| 研究開発内容                 | 直近のマイルストーン                              |   | これまでの(前回からの)開発進捗                                                                                            | 進捗度   |    |

|------------------------|-----------------------------------------|---|-------------------------------------------------------------------------------------------------------------|-------|----|

| 1<br>デバイス構造<br>設計      | 出力容量の最終目標値<br>を達成するデバイス構造<br>の設計        |   | 容量成分解析を行い、シミュレーション用のデバイス容量モデルを作成し、容量低減に向けて基礎設計を実施。デバイス構造の適正化により容量と耐圧の目標値の両立可能性を確認した。                        | 前倒し達成 |    |

| 2<br>要素プロセス<br>開発      | ・移動度: オン抵抗の目標値を満たす移動度の達成 ・TZDB: 最終仕様の達成 |   | 移動度改善に向け、移動度に影響すると考えられる各要素プロセス条件の検討を行い、目標値を実現した。また、リセス構造部のゲート膜の改善により、TZDBの目標値を達成した。                         | 前倒し達成 |    |

| 3<br>プロセスインテ<br>グレーション | 出力容量のSG1目標値<br>を達成する素子の試作ラ<br>イン構築      |   | MOS構造形成プロセス検討において実証した要素プロセスを反映したスループロセスフローを作成した。また、デバイス構造シミュレーション結果を基に出力容量の目標値を達成可能なデバイスを試作・評価し、目標の達成を確認した。 | 日標を達成 |    |

|                        |                                         | • |                                                                                                             |       | 20 |

## 2. 研究開発計画/(2) 研究開発内容(これまでの取組)

## GaNエピタキシャルプロセスの研究開発の進捗度

| 研究開発内容            | 直近のマイルストーン                        | これまでの(前回からの)開発進捗                                                                       | 進捗度   |

|-------------------|-----------------------------------|----------------------------------------------------------------------------------------|-------|

| 低欠陥化              | X線解析半値幅がSG1<br>目標値を満たすバッファー<br>形成 | AINバッファ層とSi基板界面に着目した要素プロセス検討を実施し、8インチ基板で面内全面にわたり目標値を下回るX線解析半値幅を持つ良好なバッファ層が得られることを確認した。 | 前倒し達成 |

| 大口径化              | SG1 目標値を満たす反り                     | 8インチウェハにおいて、結晶成長時の応力を制御し、AlGaN多層膜構造を開発した。同構造にて、8インチ基板で目標値を満たす反りを実現した。                  | 前倒し達成 |

| 3<br>スループット<br>向上 | 耐圧維持してプロセス時間10%削減                 | 8インチウエハにおいてAlGaN多層膜を採用し、従来の超格子構造に対して、エピ時間を10%以上削減しつつ耐圧の目標値を実現した。                       | 前倒し達成 |

### 2. 研究開発計画/(2) 研究開発内容(これまでの取組)

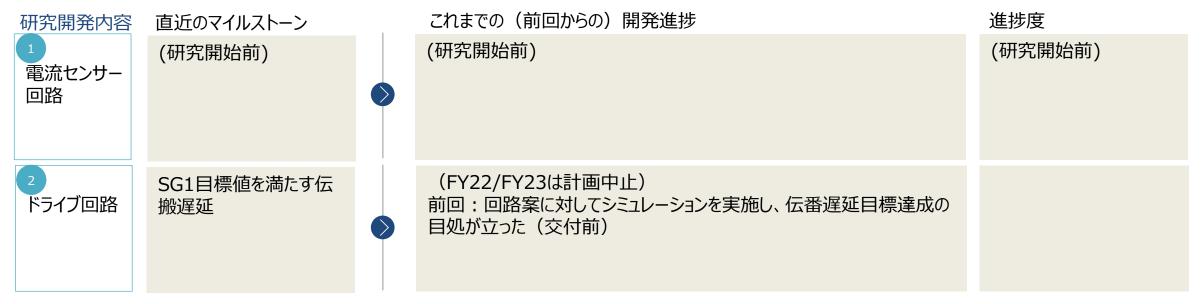

## 周辺回路技術・PoCの試作と評価の研究開発の進捗度

### 3.周辺回路技術の研究開発の進捗度

### 4.PoCの試作と評価の研究開発の進捗度

### 2. 研究開発計画/(2) 研究開発内容(今後の取組)

## ノーマリオフ型新構造GaN-FETの研究開発における技術課題と解決の見通し

| 主要デバイス特性、及び耐圧の目標値を達成するデバイス構造の設計  ・総縁膜/半導体界面特性やエピタキシャル層中のトラップ・耐圧の上のための電界緩和を実現するデバイス構造  で、耐圧の上のための電界緩和を実現するデバイス構造の設計  要素プロセスでの、しきい値の目標値、及びしきい値の目標値の達成  が一ト形状、及びゲート膜プロセスの改善・最適することでしきい値を改善することでしまい値を改善することでしまい値を改善する。・ゲート膜に係る欠陥を低減するプロセスを検討する  チャネル抵抗・出力容量積等のデバイス特性、及びゲート絶縁破壊の目標値を満たすデバイスの試作  チャネル抵抗・出力容量積と信頼性を両立するデバイス設計、および要素プロセス開発によびで検討した構造設計と②で開発したプロセス技術をスループロセスに取り込み、デバイス検証を進める。・量産対応装置を用いた試作ラインにて、制御性や再現性を確保した上で各特性、及び信頼性を両立するプロセスフローの構築する。 | 研究開発内容  | 直近のマイルストーン                            |   | 残された技術課題                        | 解決の見通し                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------|---|---------------------------------|--------------------------------------------------------------------------------|

| 要素プロセス                                                                                                                                                                                                                                                                                                                                                                                                                                           |         | 耐圧の目標値を達成す                            |   | 層中のトラップ<br>・耐圧向上のための電界緩和を実現するデバ |                                                                                |

| プロセスインテ 積等のデバイス特性、及                                                                                                                                                                                                                                                                                                                                                                                                                              | 要素プロセス  | 値の目標値、及びしきい                           |   |                                 | 慮することでしきい値を改善する                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                  | プロセスインテ | 積等のデバイス特性、及びゲート絶縁破壊の目標<br>値を満たすデバイスの試 | • | 両立するデバイス設計、および要素プロセス開           | をスループロセスに取り込み、デバイス検証を進める。<br>・量産対応装置を用いた試作ラインにて、制御性や<br>再現性を確保した上で各特性、及び信頼性を両立 |

## 2. 研究開発計画/(2) 研究開発内容(今後の取組)

## GaNエピタキシャルプロセスの研究開発における技術課題と解決の見通し

| 研究開発内容            | 直近のマイルストーン                          |             | 残された技術課題         | 解決の見通し                                                |

|-------------------|-------------------------------------|-------------|------------------|-------------------------------------------------------|

| 低欠陥化              | 表面欠陥密度、及び転<br>位密度に関して、SG2目<br>標値の達成 | <b>&gt;</b> | チャネル層および多層膜の低欠陥化 | 欠陥発生起源を解析し、構造や結晶成長条件との<br>関連を把握し、最適な構造や成長条件などを見出<br>す |

| 大口径化              | クラック長に関してSG2目標値の達成                  | •           | 応力バランスの適正化       | エピタキシャル層の構造を最適化するなど、エピタキシャル層中に形成される応力を制御する            |

| 3<br>スループット<br>向上 | 耐圧維持しつつプロセス<br>時間をSG2目標まで低<br>減     |             | エピタキシャル膜の高成長速度化  | ・成膜時のプロセスパラメータを見直し、成長速度の大きくなる結晶成長条件を精査し、プロセス時間削減を図る   |

|                   |                                     |             |                  | 24                                                    |

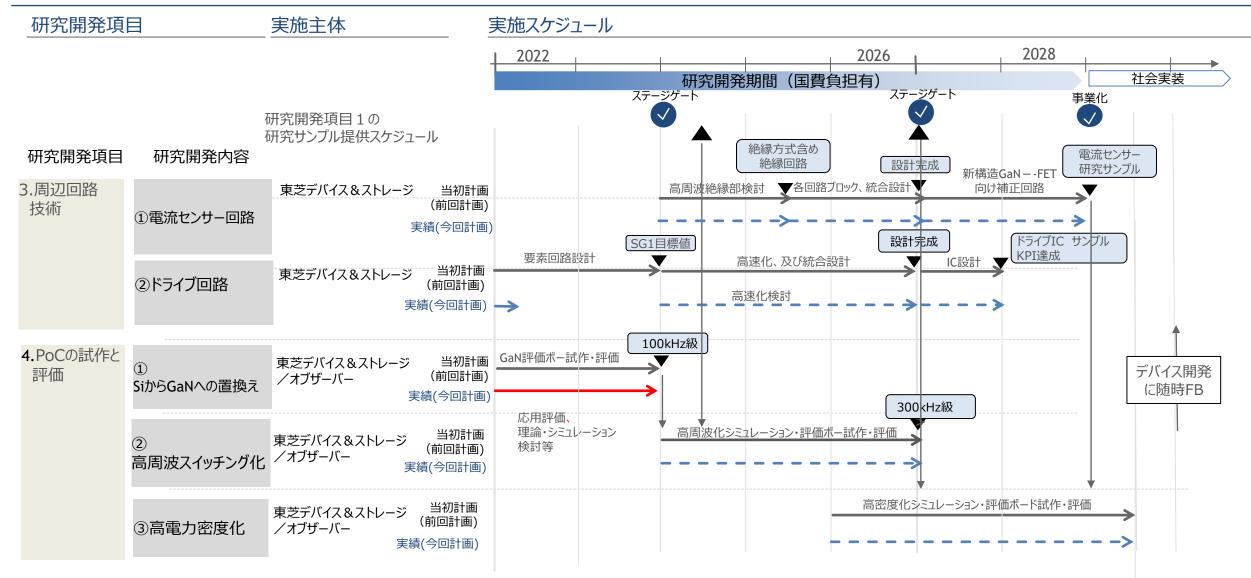

### 2. 研究開発計画/(2) 研究開発内容(今後の取組)

## 周辺回路技術・PoCの試作と評価の研究開発における技術課題と解決の見通し

### 3.周辺回路技術の研究開発の進捗度

#### 残された技術課題 解決の見通し 研究開発内容 直近のマイルストーン 広帯域化の要素回路の設計 先行研究の結果をフィードバックするとともに、シミュ 帯域に関して、目標の達 雷流セン レーションによる詳細分析と改善策を検討する サー回路 伝搬遅延の要素回路の設計 先行研究の結果をフィードバックし、シミュレーションに 伝搬遅延に関して、目標 ドライブ回 よる詳細分析と改善策を検討する の達成

### 4.PoCの試作と評価の研究開発の進捗度

研究開発内容直近のマイルストーン残さ1 Siから300kHzレベルの動作と・300kHzレベルの動作とGaNへの置損失目標の達成デバイン

残された技術課題

- ・300kHz級のスイッチング動作におけるGaN デバイス損失分析

- ・基板設計や制御など周辺を含めた損失低減

解決の見通し

GaNを用いたスイッチング評価ボードの試作および、 実測とシミュレーションによる詳細分析と改善策を検 討する

│ 換えの効果 │ 確認・課題 │ 抽出

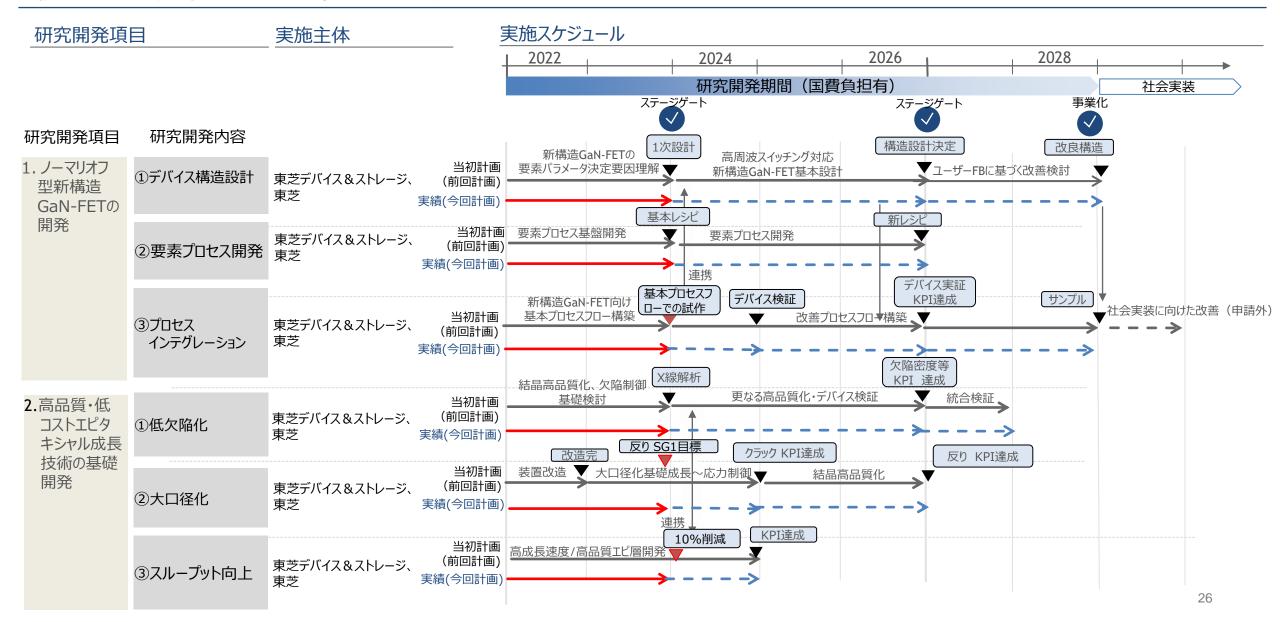

### 2. 研究開発計画/(3) 実施スケジュール

## 複数の研究開発を効率的に連携させるためのスケジュールを計画

### 2. 研究開発計画/(3) 実施スケジュール

## 複数の研究開発を効率的に連携させるためのスケジュールを計画

### 2. 研究開発計画/(4) 研究開発体制

## 各主体の特長を生かせる研究開発実施体制と役割分担を構築

### 実施体制図 次世代高電力密度産業用電源 (サーバ・テレコム・FA等) 向け GaNパワーデバイスの開発 オブザーバー社 東芝デバイス&ストレージ(株) ④PoCの試作と評価 ①ノーマリーオフ型新構造GaN-FET、 に協力、電源システムの ③エピタキシャル成長技術の基礎開発 視点でのフィードバック ③周辺回路技術 4 PoCの試作と評価を担当 ◆ オブザーバー 委託先 (株)東芝 ①ノーマリーオフ型新構造GaN-FET、 ③エピタキシャル成長技術の基礎開発 を担当

### 各主体の役割と連携方法

#### 各主体の役割

プロジェクト全体の取りまとめは、東芝デバイス&ストレージ(株)が行う

#### 研究開発における連携方法(オブザーバーとの連携)

- 東芝デバイス&ストレージ(株)とオブザーバー社は定期的に連絡会を開催し、 会社間の連絡を密に行う。

- 東芝デバイス&ストレージ(株)はオブザーバー社に対して、研究サンプルや評価ボードの提供を行う

#### デバイス要素技術開発における委託連携先

(株)東芝 研究開発センター、及び生産技術センターを委託連携先として、新構造GaN-FET、 及び関連するプロセス技術の要素技術開発を担当頂く

#### スイッチング電源のPoC試作・評価、GaN仕様へのユーザーフィードバック

• オブザーバー社は、GaN応用電源のPoC試作と評価や、デバイスへの要求仕様のフィードバックを担当する

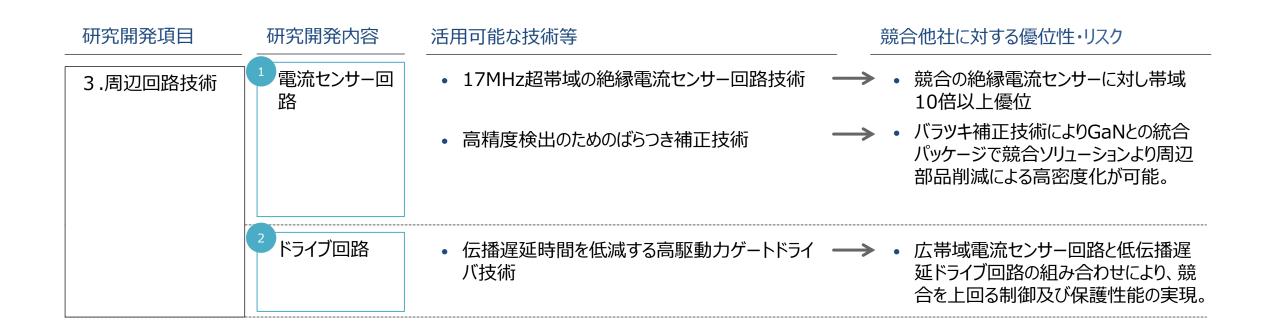

### 2. 研究開発計画/(5)技術的優位性

## 国際的な競争の中においても技術等における優位性を保有

| 研究開発項目                     | 研究開発内容                    | 活用可能な技術等                                                                                                        | 競合他社に対する優位性・リスク                                                                                                                |

|----------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| 1.ノーマリオフ型新構<br>造GaN-FETの開発 | <sup>1</sup> デバイス構造設<br>計 | <ul><li>ノーマリオンデバイスにおけるフィールドプレートを用いたデバイス設計技術</li><li>MOS型デバイスにおける電流コラプス抑制技術</li></ul>                            | <ul><li>MOSゲートと組み合わせることで、</li><li>2 DEGキャリア濃度を向上させながら、</li><li>高閾値と低オン抵抗、低容量を両立し、</li><li>デバイスの高耐圧化が可能</li></ul>               |

|                            | 変素プロセス開発・MOS構造形成          | <ul><li>高品質チャネル膜形成技術</li><li>MOS界面平滑化技術 (本PJ成果)</li><li>MOS構造最適化による閾値電圧制御技術</li><li>GaN上ゲート絶縁膜の高品質化技術</li></ul> | <ul> <li>MOSデバイスにおいて、</li> <li>世界トップレベルの高移動度チャネル形成</li> <li>高閾値と高移動度を両立</li> <li>閾値電圧変動抑制に寄与、量産レベルで<br/>ゲート信頼性実現が課題</li> </ul> |

|                            | 3 プロセスインテグ<br>レーション       | • 8インチGaN-on-Si白色LEDの事業経験                                                                                       | <ul><li>→ 8インチGaN-on-Siの量産経験、ノウ<br/>ハウの活用により、高い量産性を可能<br/>とするインテグレーション開発を短期間<br/>で実施することが可能</li></ul>                          |

### 2. 研究開発計画/(5)技術的優位性

## 国際的な競争の中においても技術等における優位性を保有

| 研究開発項目                                 | 研究開発内容               | 活用可能な技術等                                                              | 競合他社に対する優位性・リスク                                                                 |

|----------------------------------------|----------------------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 2.高品質・低コスト<br>エピタキシャル成<br>長技術の基礎開<br>発 | 1 低欠陥化               | <ul><li>中間層を用いた欠陥制御技術</li><li>界面制御による高品質バッファー技術<br/>(本PJ成果)</li></ul> | <ul><li>Si基板上GaN結晶で世界トップレベルの低転位密度実現</li><li>高品質なAINバッファを形成可能</li></ul>          |

|                                        | 2<br>大口径化<br>(8インチ化) | <ul><li>バッファ層技術</li></ul>                                             | > • 他社に比べ高い応力制御性、8インチ<br>基板での反り抑制が可能                                            |

|                                        |                      | • GaN結晶中の応力制御技術                                                       | <ul><li>結晶中に生じる応力を制御でき、応力<br/>バランスの適正化、反り抑制が可能</li></ul>                        |

|                                        |                      | • 低欠陥GaN形成技術                                                          | > • 低欠陥化と反り抑制の両立が可能                                                             |

|                                        |                      | 8インチGaN-on-Si白色LEDの事業経験                                               | <ul><li>8インチGaN-on-Siの量産経験、ノウ<br/>ハウの活用により、量産プロセスを考慮<br/>した要素技術の開発が可能</li></ul> |

|                                        | 3 スループット向上           | <ul><li>高品質結晶成長技術</li><li>8インチGaN-on-Si白色LEDの結晶成長プロセ</li></ul>        | > • 積層欠陥を抑制する結晶成長技術を<br>基に高速成膜技術を開発し、高品質<br>かつ高スループットを実現可能                      |

|                                        |                      | ス時間短縮の知見、ノウハウ                                                         | > • 量産経験・ノウハウの活用により、高品質かつ高スループット化が可能                                            |

### 2. 研究開発計画/(5)技術的優位性

## 国際的な競争の中においても技術等における優位性を保有

# 3. イノベーション推進体制

(経営のコミットメントを示すマネジメントシート)

## 3. イノベーション推進体制/(1)組織内の事業推進体制

## 経営者のコミットメントの下、専門部署に複数チームを設置

### 組織内の役割分担

#### 研究開発責任者と担当部署

- 研究開発責任者

- 先端半導体デバイス開発センター長:端半導体デバイス開発を統括

- 担当チーム

- チームA: ①新構造GaN-FETの開発を担当

- チームB: ②GaN内製エピ開発担当

- チームC: ③周辺回路・電源PoC開発担当

- アプリ応用担当 (シニアフェロー):

ソリューション開発・オブザーバー社窓口

- -姫路半導体工場(工場長):開発・試作ライン整備

- -社会実装担当(製品技術シニアマネジャー):

社会実装に向けたマーケティングと製品技術を統括

- チームリーダー

- チームA 先端デバイス開発マネジャー: GaN-HEMT開発の実績

- チームB 先端プロセスエキスパート: GaNエピ開発等の実績

- チームC ソリューション開発スペシャリスト:回路の機能仕様策定の実績

#### 部門間の連携方法

- PJ月例会議(1回/月、開発進捗管理、チーム間情報連携)

- トップ報告(1回/月、事業部長/関係者に報告)

- 情報共有会(1回/週、主任研究者/スタフを中心に情報共有)

- PJ専用のデータベースを設置し、関連情報を一元管理

連携

※ CSO:Chief standardization officer-最高標準化責任者

### 3. イノベーション推進体制/(2)マネジメントチェック項目① 経営者等の事業への関与

## 経営者等による当該プロジェクト事業への関与方針

### (1)経営者等による具体的な施策・活動方針

- 経営者のリーダーシップ

- 社外ホームページで環境方針を社長コミットメントとして公表

- 東芝デバイス&ストレージ株式会社グループは、東芝グループの経営理念である「人と、 地球の、明日のために。」に基づき、豊かな価値の創造と地球との共生を図ります。また、 脱炭素社会、循環型社会、自然共生社会を目指した環境経営により、持続可能な 社会の実現に貢献し、新しい未来を始動させます。

https://toshiba.semicon-storage.com/jp/company/about/environment/statement-of-environmental-philosophy.html

- 半導体事業部門のトップとしてwebでメッセージ発信

- 半導体はシリコンを材料とするものがほとんどだが、高い電圧や高速な動作など一部の 用途では、シリコンで実現できる性能に物理的な限界が訪れようとしている。そこで次世 代のパワー半導体として注目されているのが、炭化ケイ素(SiC)や窒化ガリウム (GaN) などの化合物半導体である。シリコンのパワー半導体に比べて、飛躍的な性 能の改善が期待されている。具体的には、電力効率が改善することで機器の消費電 力を大幅に削減したり、システムの小型化にも寄与したりすることができる。

https://www.toshiba-clip.com/detail/p=4809

- 事業のモニタリング・管理

- 進捗状況のフォロー研究開発および事業の進捗状況は、取締役社長および担当取締役が出席する月次マネジメント会議の場で定期的にフォローされ、必要により、計画見直し等の意思決定、進め方・内容に対しての指示を行う。

- 株式会社東芝との連携 事業の進捗を判断するにあたり、親会社の株式会社東芝からの意見も取り入れる。

- 事業化の判断 投資回収計画、ROS、及び市場・競合状況等から総合的に判断する。

### (2)経営者等の評価・報酬への反映

業績評価 事業の進捗状況や成果が、事業部の担当取締役・担当管理職等の評価や報酬の一部 に反映される。

### (3) 事業の継続性確保の取組

事業の引き継ぎ

経営層が交代する場合は、担当管理職等から事業内容について着実に説明を行うことで、 事業が継続し、意思決定に支障をきたすことのないように進める。

### 3. イノベーション推進体制/(3)マネジメントチェック項目② 経営戦略における事業の位置づけ

### 経営戦略の中核にパワー半導体事業を位置づけ、企業価値向上とステークホルダーとの対話を推進

### (1)中期計画検討会/経営会議等での議論

#### カーボンニュートラルに向けた全社戦略

- カーボンニュートラルに貢献する関連製品ポートフォリオの中計等での立案、経営会議/取締役会での承認をはじめ、自社製造拠点での100%再エネ化、バリューチェーン全体でのカーボンニュートラル実現を目標に掲げる

https://toshiba.semiconstorage.com/jp/company/about/environment/making-carbon-neutrality-a-reality.html

#### ・ 経営戦略への位置づけ、事業戦略・事業計画の決議・変更

- 関連製品の開発ロードマップ等の策定/見直しを行い、中期計画に反映、その 内容を経営会議/取締役会で承認、事業方針説明会や中計説明会等で関 連部署に周知した

- 非上場化により事業環境が変化するが、開発ロードマップを含めた製品ポートフォリオはそのまま変更せず、計画通り進めていく事を確認している

- 研究開発は事業の根幹であり、その計画は不可欠な要素として、優先度高く 位置付けている

#### コーポレートガバナンスとの関連付け

- 事業戦略に基づいた取締役や管理職が選任されるとともに、進捗状況や成果が、事業部の担当取締役・担当管理職等の評価や報酬の一部に反映されている

### (2) ステークホルダーとの対話、情報開示

#### 中長期的な企業価値向上に関する情報開示

- (株)東芝の統合報告書等において経営理念に基づいたカーボンニュートラルによる 持続可能な未来の実現をうたい、それらを達成する全体としての事業戦略等を開 示している

- 自社ウェブサイトでの情報発信 化合物半導体を含むパワー半導体事業における自社の取り組みについて、自社ウェブサイトを活用し、ステークホルダーや顧客を含む一般の方々に対し、幅広く分かりやすい情報発信を行う。併せて展示会等に出展してPRしている

#### <情報発信の具体例>

・TECHNO-FRONITER2023に出展

「TECHNO-FRONTIER 2023」への出展について | 東芝デバイス&ストレージ株式会社 | 日本 (semicon-storage.com)

Web HPでの発信

性能と使いやすさを両立したGaNパワーデバイス | 東芝デバイス&ストレージ株式会社 | 日本 (semicon-storage.com)

日経XTECHによる発信

東芝が2023年のGaNデバイス発売に向け、差異化回路技術を開発 | 日経クロステック(xTECH) (nikkei.com)

#### 企業価値向上とステークホルダーとの対話

- (株)東芝の中期目標として、全体としての各種財務指標を目標として位置づけ、 その改善には事業ポートフォリオの変更等の方策をとっている

- 投資家や金融機関等のステークホルダーに対し、技術戦略説明会を開催し当社 の化合物半導体を含むパワー半導体事業の将来見通し・リスクを説明している

### 3. イノベーション推進体制/(4)マネジメントチェック項目③事業推進体制の確保

### 機動的に経営資源を投入し、着実に社会実装、企業価値向上に繋ぐ組織体制を整備

### (1)経営資源の投入方針

- 全社事業ポートフォリオにおける本事業への人材・設備・資金の投入方針

- 本プロジェクトを含むパワー半導体は注力領域であることに変わりなく、統合報告書にもパワー半導体の重要性とカーボンニュートラルの実現い貢献する旨を謳っている。

https://www.global.toshiba/jp/ir/corporate/library/annual-report.html

- GaN事業については、中期計画に織り込み、資金投入の継続性について 社内的合意を形成している

- GaNの事業化に向けて人材・設備・資金を投入する方針に変更はなく、 設備投資、研究開発費、人材強化等に自己資金を投下した。

- ・新卒およびキャリア採用、配置転換により、人材強化を実施した。

- ・既存工場内に試作の場所を確保し、装置の設置を開始した。

- ・装置導入を中心に投資を実施した。

- 機動的な経営資源投入、実施体制の柔軟性確保

- 23年4月の組織変更にて、化合物半導体開発部門を集結し、デバイス 一体となった開発体制を整えた。

- 生産を見据えた開発ラインの構築を開始した。

#### (2)組織横断体制の構築、人材育成

- 組織横断体制の構築

- 機動的な意思決定 当該事業を遂行するため、組織横断で人員を集結しプロジェクト体制を 構築し、機動的な意思決定を可能な体制としている。

- 事業環境の変化への対応 組織横断のプロジェクト体制により、既存の組織体制や事業体制にとら われず、柔軟にビジネスモデルの検証を行い、事業環境の変化への対応 を可能とする。

#### • 人材育成

- 若手チームメンバーの起用若手人材を積極的にチームメンバーに起用し、プロジェクト活動の中で技術的育成を図る。

- 技術報告や論文提出の機会の活用 本プロジェクトの技術成果について、技術報告書や論文等の形で社内 外に発信することを支援し、技術者としての能力向上を図っている。

- 展示会への出展 技術者が直接顧客に接して生の**VoC**に触れる機会を得ることで、提案 力向上等を図っている。

# 4. その他

### 4. その他/(1) 想定されるリスク要因と対処方針

## 想定されるリスクと対応および事業中止の判断基準

### 研究開発(技術)におけるリスクと対応

- 装置開発遅れによるデバイス開発の遅延

- → 装置ベンダとの協調、連携強化

- SiやGa2O3の想定外の技術革新により、GaNの競 争力が相対的に低下

- → 技術動向を調査し、適宜目標や検討アイテ ムの見直しを行う

- 目標とする機能・性能が確保できないリスク

- → 期毎にKPIを設定し技術開発進捗を管理し、目標 達成の確度を向上、フォローアップしていく

### 社会実装(経済社会)におけるリスクと対応

- ・ 高周波スイッチング回路の周辺部品価格高騰による・ Ga原材料の高騰(地政学的に) GaN電源市場伸長の停滞

- → 部品メーカーとの連携模索

- ・ 投資回収計画の破綻

- 市場停滞

- → スイッチング電源以外の市場への展開

- 競合他社に対しての遅れによる参入機会損失

- → ベンチマークにより立ち位置の確認を実施 すると共に、必要に応じたリソース増強、他 計連携

- その他(自然災害等)のリスクと対応

- - → 調達先との連携

- データセンターレイヤのパラダイムシフトによる 産業構造の大変化

- → 他市場への展開

- 大地震などの自然災害により研究継続不可

- →関東地区と近畿地区の2拠点での開発など の工夫

- 事業中止の判断基準:

- ・ 災害や、グローバル経済の悪化などの事業環境変化により、計画通り自己資金投下が不可能になった場合

- ・ 当初計画より投資回収に著しい遅れが生じた場合