# 事業戦略ビジョン

実施プロジェクト名: 次世代デジタルインフラの構築プロジェクト

【研究開発項目3】次世代グリーンデータセンター技術開発

研究開発内容 ② 光に適合したチップ等の高性能化・省エネ化技術の開発/省電力CPU開発

実施者名 : 富士通株式会社(幹事会社) 代表名:代表取締役社長 時田 隆仁

共同実施者: アイオーコア株式会社

日本電気株式会社キオクシア株式会社

富士通オプティカルコンポーネンツ株式会社

京セラ株式会社

# 目次

- 0. 共同実施における各主体の役割分担

- 1. 事業戦略・事業計画

- (1) 産業構造変化に対する認識

- (2) 市場のセグメント・ターゲット

- (3) 提供価値・ビジネスモデル

- (4) 経営資源・ポジショニング

- (5) 事業計画の全体像

- (6) 研究開発・設備投資・マーケティング計画

- (7) 資金計画

- 2. 研究開発計画

- 2.1 共同実施による研究開発内容

- (1) 研究開発目標

- (2) 研究開発内容

- (3) 実施スケジュール

- (4) 研究開発体制

- (5) 技術的優位性

- 2.2 省電力CPU開発

- (1) 研究開発目標

- (2) 研究開発内容

- (3) 実施スケジュール

- (4) 研究開発体制

- (5) 技術的優位性

- 3. イノベーション推進体制(経営のコミットメントを示すマネジメントシート)

- (1) 組織内の事業推進体制

- (2) マネジメントチェック項目① 経営者等の事業への関与

- (3) マネジメントチェック項目② 経営戦略における事業の位置づけ

- (4) マネジメントチェック項目③ 事業推進体制の確保

- 4. その他

- (1) 想定されるリスク要因と対処方針

# 0. 共同実施における各主体の役割分担

# 共同実施各社の研究開発内容および社会実装への取り組み

#### 富士通(株) 富士通(株) アイオーコア(株) 京セラ(株) 日本電気(株) キオクシア(株) 富士通オプティカル **コンポーネンツ(株)** ①23の共同実施※ ①-2の共同実施 研究開発の内容 研究開発の内容 研究開発の内容 研究開発の内容 研究開発の内容 研究開発の内容 研究開発の内容 ・光電融合デバイス開発 CPO適用技術、レイ ・高変調効率光エンジン ・光電集積デバイスパッ • 省電力CPU開発 省電力アクセラレータ • 広帯域 SSD 開発 技術の開発 を担当 ヤ1ソフトフレーム処理 ケージング技術の開発 を担当 開発 を担当 技術の開発 を担当 を担当 • ディスアグリゲーション 技術の開発 を担当 を担当 社会実装に向けた 社会実装に向けた 社会実装に向けた 社会実装に向けた 社会実装に向けた 社会実装に向けた 社会実装に向けた 取組内容 取組内容 取組内容 取組内容 取組内容 取組内容 取組内容 • DC、HPCなどのサーバー ・ 消費電力を大きく減少さ ・開発加速に向けたオープ • 研究開発成果を光電集 • 持続可能な社会を実現 ・自社のDC・サーバ製品 データセンタを中心に、 上短距離通信における せる『光スマートNIC』を ンイノベーションの推進 積モジュールとして事業 するサービスを支えるプ に事業展開 「広帯域SSD技術」の PCIe6.0対応の配線と 開発し、グリーンでスマー • 製品力を高めるための製 の構築 ラットフォームに適用 • 一部のソフトウェアは マーケティング活動をグ トな社会の創出に貢献 • モジュール構成部品 ローバルに展開 して実用化 造プロセスの強化 OSSとし、マネジメント • チップ間接続の消費電力 富士通と連携しての標 (基板、コネクタ、等) • 超低消費電力を武器に サービスを展開 ディスアグリゲーション技 する 術への適応・対応による、 を電気配線と比較して POCにより潜在顧客の 準化、マーケティングの推 を切り出して電子部品 データセンターやHPC向 協議会で省エネコンポー 進 90%削減 ニーズを確認し、開発計 市場に製品展開 けの省電力CPUとして普 ネントとそのI/Fを訴求し、 SSD・ストレージシステム 画に反映 及を図る WWのDC市場に製品を 電力効率の向上推進

※②-3不揮発メモリを除く

★ 研究開発項目3 幹事企業

☆ 研究開発内容①-2とりまとめ企業

展開

# 1. 事業戦略·事業計画

## 1. 事業戦略・事業計画/(1)産業構造変化に対する認識

# データセンターに求められる省電力性、富士通の役割

### カーボンニュートラルを踏まえたマクロトレンド認識

- AI・ビッグデータの産業利用が進展

- ■データセンターの計算能力と省電力性に対する需要が増加

# 社会

- 再生可能エネルギーの利用が拡大

- Society5.0\*の実現や、5Gなどの通信技術の活用、ビッグデータ・AI 情報基盤の整備が進展

# • 近年、欧州を中心とした多くの炭素税導入国においてさらなる税率引き上げが見込まれる

• 今後、さらにICTの電力が増大し、そのうちデータセンターが占める割合 も増大する予測

# 経産省エネルギー基本計画にて温室効果ガス削減目標が46%に引き上げ(2021年4月)

• デジタルニューディールにより5G、クラウドサービス、HPC(高性能計算機)等の利活用が増加

技术

• ネットワーク接続された機器数、データ総量が飛躍的に増大する予測

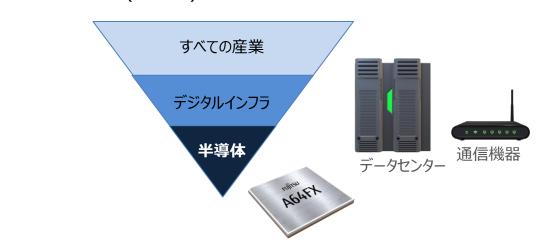

### カーボンニュートラル社会における産業アーキテクチャ

■ 省電力CPU(半導体)は、デジタル社会を支える重要基盤

\*: Society5.0

サイバー空間(仮想空間)とフィジカル空間(現実空間)を高度に融合させたシステムにより、経済発展と社会的課題の解決を両立する、人間中心の社会(Society) 狩猟社会(Society 1.0)、農耕社会(Society 2.0)、工業社会(Society 3.0)、情報社会(Society 4.0)に続く、新たな社会を指すもの

富士通はCPUの性能及び省電力性を実現するマイクロアーキテクチャを富士通研究開発部門が設計をしており、この技術とノウハウの活用により、スーパーコンピュータ「富岳」において世界トップレベルの高性能・省電力を達成している

「富岳」で開発したCPU(A64FX)開発メンバーにより、富士通が持つ技術・ノウハウを一層の深化をさせるとともに、標準化への対応などの探索活動により、次世代グリーンデータセンターに適応する省電力CPUを開発し、その普及を図るためのエコシステムを確立する

# 1. 事業戦略・事業計画/(2) 市場のセグメント・ターゲット

# データセンター/クラウドサービス・HPC市場をターゲットに設定

### セグメント分析

高性能・低消費電力ニーズが強い、HPC・データセンター市場において、①データセンター/クラウドサービス、②HPCアプリを支えるサーバを提供

### ターゲットの概要

### 市場概要

①データセンター/クラウドサービス向け:データセンター市場をターゲットとする

②HPC向け:研究機関向けHPC市場をターゲットとする

| 市場ターゲット              | 主なプレー<br>ヤー                                              | 課題                                                                                                                  | 想定ニーズ                                                                                             |

|----------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| データセンター/<br>クラウドサービス | Amazon<br>Microsoft<br>Google<br>Fujitsu<br>Yahoo<br>IIJ | <ul> <li>x86ロックイン*2回避</li> <li>ユーザ需要に応じたコンピューティングパワー提供</li> <li>データセンターの環境負荷低減、運営費の削減</li> <li>セキュリティの確保</li> </ul> | <ul> <li>Arm CPU</li> <li>成長領域(データ解析、AI)の<br/>処理性能</li> <li>低消費電力</li> <li>セキュリティ機能の強化</li> </ul> |

| 研究機関向け<br>HPC        | 大学、<br>研究所、<br>民間企業の<br>研究部門                             | <ul><li>施設の電力範囲内で高い<br/>処理性能の実現</li></ul>                                                                           | <ul><li>科学技術計算・AI計算に対する高い並列処理性能</li><li>低消費電力</li></ul>                                           |

\*1: ODM(Original Design Manufacturing) Direct 委託者のブランドで製品を設計・生産するベンダから直接コーザーに出荷すること

\*2:x86ロックイン

Intel製x86アーキテクチャCPU搭載製品に依存し、他CPU搭載製品に乗り換えできない状態

# 1. 事業戦略・事業計画/(3) 提供価値・ビジネスモデル

# 高性能・低消費電力CPUを活用したビジネスを展開

### 社会・顧客に対する提供価値

- Society 5.0時代の大量データ処理を可能とする **巨大なコンピューティングパワー**

- 未来社会を支えるトラスト基盤としての 高い安定性とセキュリティ

- カーボンニュートラルの実現に向けた電力 削減を可能とする**高い電力性能**

### 【次世代データセンター CPUの特徴】

| 高性能        | <ul><li>データ解析・シミュレーションにフォーカスした設計により向上</li><li>大量データ処理のための圧縮技術による通信性能向上</li></ul>                        |  |  |  |

|------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| 高い<br>電力性能 | <ul> <li>データ解析・シミュレーション領域に<br/>おける電力性能向上によりCO2削<br/>減に貢献</li> <li>ランニングコストを削減し、高い経<br/>済性を実現</li> </ul> |  |  |  |

| 高い<br>信頼性  | <ul><li>メインフレームで培った安定稼働技術</li><li>富士通設計開発による安全保障への貢献</li></ul>                                          |  |  |  |

| 使い<br>やすさ  | <ul><li>サービス・ソフト・ハードによるコデザインにより対応アプリ拡大</li></ul>                                                        |  |  |  |

ビジネスモデルの概要(製品、サービス、価値提供・収益化の方法)と研究開発計画の関係性

### 【データセンター/クラウドサービス】

- **巨大なコンピューテイングパワーが必要なAI・データ解析・シミュレーション**に、大量データ処理能力に特徴を持つ**超低消費電力 CPU**を投入しサービスビジネスを拡大

- 富士通開発プロセッサにより、社会を支えるトラスト基盤として、システムの安定性・データ保全を担保

- 社内・社外SIerを巻き込み、高い電力性能を武器にデータセンターへ浸透し、省電力データセンターの普及に繋げ環境問題に貢献

### [HPC]

- 超低消費電力を武器に**研究機関向けHPC**など、従来プロダクトビジネスも継続して獲得

- ・ 従来型のHPCからAI/データ解析の融合領域へ拡大

### 【ビジネスモデルの特徴】

• 最大の特徴である**富士通開発の高性能・超低消費電力CPU**と富士通の強みである<u>ハードからサービスまでを垂直統合した製品提</u> 供力を掛け合わせ、他社には真似できない高付加価値なサーバ、サービスを提供

### 【必要となる研究開発】

• ビジネスの中心となるCPUの革新的な省電力化に複数の高度な省電力化技術の開発とそれらを同時実装する必要がある

### 【サプライチェーンへの波及効果】

- データセンターの電力性能を向上し、これまでにない高速なデータ解析や画像診断等の高度なAI産業利用による<u>迅速で高度な意思</u> **決定**を可能とすることで、国内産業の活性化、国際競争力の強化を推進

- x86ロックインを打破し、市場競争の健全化のためにも、Armアーキテクチャベースのデータセンター向け省電力CPUの普及を図る

# 1. 事業戦略・事業計画/(4)経営資源・ポジショニング

# 高性能・低消費電力CPU開発力を活かして、環境に配慮したコンピューティングパワーを提供

### 自社の強み(経営資源)

### ターゲットに対する提供価値

- Society5.0時代の大量データ処理を可能とする巨大なコンピューティングパワー

- 未来社会を支えるトラスト基盤としての高い安定性とセキュリティ

- カーボンニュートラルの実現に向けた電力削減を 可能とする高い電力性能

### 自社の強み

- 世界トップレベルの高性能・低消費電力プロセッサ 開発力

- メインフレームで培った安定稼働技術を取り入れ、 富士通設計により技術の透明性を確保したCPU を提供可能

- ハードからサービスまで垂直統合した製品提供力

- 国内サーバ売上1位(2021年度)\*の幅広い販路

### 自社の弱み及び対応

海外販売チャネル 既存の海外顧客に加えて、新規顧客獲得のため、 他社アライアンスによる販路開拓を検討

### 他社に対する比較優位性

|             | 技術                                                     | 顧客基盤(現在)                                                   | その他経営資源                                                                      |  |  |  |  |  |  |

|-------------|--------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|--|--|

| 富士通         | 省電力設計技術<br>※世界1位の電力性<br>能CPU(A64FX)開発<br>実績            | HPC(国内中心、<br>Arm/x86)<br>データセンター(国内、<br>x86)               | x86サーバ事業<br>Sier(システム開発)<br>富士通データセンター                                       |  |  |  |  |  |  |

| A社<br>(x86) | 自社CPU製造、パッケージング技術,特定<br>用途向けアーキテクチャ<br>改善による省電力化な<br>ど | HPC(国内/海外)<br>データセンター(国内/<br>海外)<br>※自社CPU搭載装<br>置ベンダの顧客基盤 | NIC(ネットワークインター<br>フェースカード)、FPGA、<br>SSD、周辺LSIなどの幅<br>広いサーバ・PCのコン<br>ポーネントを提供 |  |  |  |  |  |  |

| B社<br>(x86) | パッケージング技術、特<br>定用途向けアーキテク<br>チャ改善による省電力<br>化など         | HPC(国内/海外)<br>データセンター(国内/<br>海外)<br>※自社CPU搭載装<br>置ベンダの顧客基盤 | GPU、周辺LSIなどの<br>サーバ・PCのコンポーネン<br>トを提供                                        |  |  |  |  |  |  |

| 他社比較        | データ解析・シミュレー<br>ション領域において優位<br>な電力性能                    | x86サーバ事業の国内<br>販路を活用<br>他社アライアンス締結<br>による海外HPC販路<br>開拓を検討  | ハードからサービスまで垂<br>直統合した製品を提供<br>可能                                             |  |  |  |  |  |  |

<sup>\*</sup> https://www.fujitsu.com/jp/products/computing/servers/news/idcserver-research.html?from=server\_sbnr01

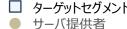

# 1. 事業戦略・事業計画/(5) 事業計画の全体像

6年間の研究開発の後、2027年度に事業化、2030年度に投資の回収を計画

### 投資計画

- 本事業の支援期間で、約750億円規模の研究開発費を計画

- 本事業終了後も研究開発を継続し、省電力CPU搭載製品の事業化を目指す

- ・ 日本国内、海外市場での販売を図り、2030年までに投資回収するととも、社会実装を促進することにより

# 1. 事業戦略・事業計画/(6)研究開発・設備投資・マーケティング計画

# 研究開発段階から将来の社会実装(設備投資・マーケティング)を見据えた計画を推進

### 研究開発·実証

### マーケティング

## 取組方針

- 省電力設計技術はクローズ戦略

- データ解析・シミュレーションにフォーカスした設計を実施

- ファームウェア/ソフトウェアインターフェースは業界標準仕様やArm標準仕様を採用

- 強固なセキュリティ対策をCPUアーキテクチャに反映

- コンソーシアム(OCP\*1, IOWN Global Forum\*2

等)の議論の参照や技術提案を検討

- 半導体製造ファウンドリにCPU製造を委託することで、設備投資を抑えながら、安定した調達を実現

設備投資

- 既存の国内販路を活用し販路拡大

- 学会、展示会などでCPU/サーバ仕様、プロトタイプをもとに訴求

## 国際競争 上の 優位性

- 省電力設計技術はクローズ戦略とし、データ解析・シミュレーション領域において、高い電力性能による差別化を 実現

- データ解析・シミュレーション領域において高性能を実現

- OSS(オープンソースソフトウェア)活動やArmコミュニティに 貢献し、Armエコシステムの拡大、市場形成に貢献

- コア技術以外のCPU周辺技術は標準仕様に準拠

- クラウド/データセンターに必要とされる強固なセキュリティを 実現

- システム構築が可能な富士通の強みを活かした、垂直統 合モデルを確立

- コンソーシアムにおける、議論や技術提案によりプレゼンスを発揮し、戦略的な連携を模索

- 半導体製造ファウンドリの最先端 プロセスと富士通の省電力設計 技術を組み合わせ、データ解析・ シミュレーション領域において、高 い電力性能を実現。

- 海外プレーヤーとの戦略的な連携を確立し、幅 広い販路を確保

- 電力性能比、価格性能比の他社比較数値を 学会や展示会などでアピールし、新規顧客を開 拓

- \*1: OCP (Open Compute Project)

スケーラブルなコンピューティングを実現するために、最も効率の良いサーバや ストレージ、データセンターなどのハードウェアを設計、提供することを目指す活動

\*2: IOWN (Innovative Optical and Wireless Network) Global Forum 最先端の光技術を使って、豊かな社会を創るための構想を議論する場

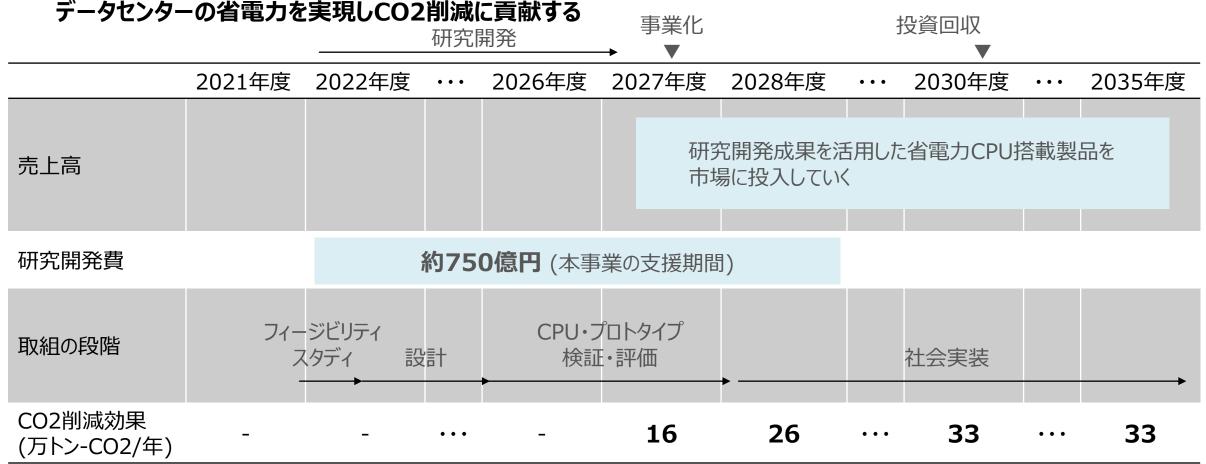

# 1. 事業戦略・事業計画/(7)資金計画

# 国の支援に加えて、250億円以上の自己負担を予定

### 資金調達方針

- 本事業では、国費負担だけでなく、富士通として研究開発投資の一部と社会実装のためのその他関連投資を予定している

- 富士通は、本事業終了後も研究開発を継続し、省電力CPU搭載製品の事業化とその普及のためのエコ システムの確立を目指す

# 2. 研究開発計画

# 2.1 共同実施による研究開発内容

# 2.1 共同実施による研究開発内容/(1)研究開発目標

# DCの省力化40%以上というアウトプット目標を達成するために必要な複数のKPIを設定

### 研究開発項目 アウトプット目標 2030 年までに、研究開発開始時点で普及しているデータセンターと比較して 40%以上の省エネ 【研究開発項目3】 化を実現 次世代グリーンデータセンター技術開発 研究開発内容 KPI設定の考え方 **KPI** ・PCIe6.0 に対応した光トランシーバを開発 DCの4.4%の電力消費が電気配線であり、光配線化することで配線に 光電融合デバイス開発 ・チップ間接続の消費電力を電気配線と比較して 関わる電力を1/10までに削減する 90%削減 1 -2 ・ビットあたり消費電力を従来比で1/10へ削減 現行の光伝送装置の消費電力から、CPO技術適用とレイヤ1ソフトフ 光スマートNIC開発 レーム処理技術適用によりビット当たりの消費電力1/10を実現する 2 -1 ・現行自社CPUに対し10倍の電力効率向上 DCの省力化40%以上を達成するためには、消費電力占有率が最も 省電力CPU開発 高いCPUの電力効率を10倍に改善する高い目標設定が必要 ・現行汎用CPU比10倍の電力効率、メモリ帯域 -2 アクセラレータで利用するアプリで現行汎用CPU比10倍の電力効率。複 省電力アクセラレータ開発 数チップレット(複数HBM搭載)の構成で5TB/s以上のメモリ帯域を 5TB/s以上 実現する ・連続リード性能(或いは帯域)を現行(PCIe® Gen.3 サーバーの電力効率を向上させるためにはストレージの広帯域化が必要。 広帯域 SSD 開発 世代相当)から8倍にする 2028年にストレージシステムとして128GB/sを達成する ・制御対象機器の利用効率の最適化により、制御 ワークロード特性に対応した動的構成変更により、最適なリソースを割り ディスアグリーゲーション技術の開発 対象機器を制御しない場合と比較して消費電力 当て、不要部分の電力を削減することで消費電力を20%程度改善 20%の削減

※PCIe は、PCI-SIG の登録商標です。

# 2.1 共同実施による研究開発内容/(2)研究開発内容

# 各KPIの目標達成に必要な解決方法を実施

|                                              | KPI                                                  | 現状                                             | 達成レベル                                                      | ı | 解決方法                                                                                                                                  | 実現可能性 (成功確率)                                  |

|----------------------------------------------|------------------------------------------------------|------------------------------------------------|------------------------------------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| 1 -1<br>光電融合デバイス開発                           | ・PCIe6.0 に対応<br>・電気配線と比較して<br>電力 90%減                | 電子回路等の要素技術(TRL4)                               | 信頼性・量産性を<br>満足した製品レベ<br>▶ル(TRL9)                           |   | <ul><li>低損失シリコンフォトニクス回路技術</li><li>① リニアリティの高い光素子による高速PCle6.0</li><li>(32GBau,PAM4)</li><li>② 電子回路のCDRが不要となり低電力化</li></ul>             | 低損失シリコンフォト<br>ニクス回路の適用に<br>より高い実現可能性<br>(90%) |

| 1 -2<br>光スマートNIC開発                           | ビットあたり消費電力<br>を従来比で1/10へ削<br>減                       | レイヤ1ソフトフ<br>レーム処理技術<br>は研究開発段<br>階(TRL2)       | 製品一歩手前の<br>プロトタイプ機の<br>➤ 完成(TRL6)                          |   | <ul> <li>システム、部品、集積の3要素技術を集結</li> <li>システム: CPO適用技術、レイヤ1ソフトフレーム処理技術</li> <li>部品:高変調効率光エンジン技術</li> <li>集積:光電集積デバイスパッケージング技術</li> </ul> | 世界最高水準の技<br>術を持つ3社の集結<br>で成功確率は高い<br>(80%)    |

| <sup>2</sup> -1<br>省電力 CPU 開発                | 現行自社CPUに対し<br>10倍の電力効率向<br>上                         | 一部の技術開<br>発項目において、<br>原理確認段階<br>(TRL1)         | 技術開発の検<br>証・評価と、後半<br><b>→</b> の実証システムに<br>向けた試作<br>(TRL4) |   | <ul><li> 富岳で採用した省電力回路設計技術を進化</li><li> 省電力につながる新しいデバイスの取り込みや、テクノロジを開発</li></ul>                                                        | 原理確認段階の開<br>発項目がある為<br>(60%)                  |

| <ul><li>2 -2<br/>省電力アクセラレータ<br/>開発</li></ul> | 現行汎用CPU比10<br>倍の電力効率、メモリ<br>帯域5TB/s以上                | 汎用CPU比5倍<br>の電力効率、メ<br>モリ帯 1.5TB/s ←<br>(TRL4) | 汎用CPU比10<br>倍以上の電力効<br>■ x、メモリ帯域<br>5TB/s以上<br>(TRL5)      |   | <ul><li>ベクトル・アーキテクチャの機能強化やチップ内部のマイクロ・アーキテクチャ改良による電力効率向上</li><li>チップレット設計によるメモリ帯域5TB/s 構成の実現</li></ul>                                 | 所望アプリのベンチ<br>マーク電力当たり性<br>能改善<br>(70%)        |

| 2 -4<br>広帯域 SSD 開発                           | 連続リード性能(或いは<br>帯域)を現行(PCIe®<br>Gen.3世代相当)から<br>8倍にする | PCIe <sup>®</sup> Gen3<br>相当(TRL3)             | PCIe® Gen6<br>相当(TRL7)                                     |   | <ul> <li>光インターフェイスブリッジの最適実装,ディスアグリゲーション対応ストレージ管理SW開発</li> <li>方式① 最適帯域となる管理SW</li> <li>方式② 低電力CPUで管理SW実行</li> </ul>                   | 達成レベルに未達の<br>可能性あり<br>(70%)                   |

| 3<br>ディスアグリゲーション<br>技術の開発                    | 効率の最適化により、<br>制御対象機器を制御<br>しない場合と比較して<br>消費電力20%の削減  | (TRL3)                                         | コンポーネント単<br>位のAP要求性<br>● 能に応じた動的<br>自動構成変更<br>(TRL7)       |   | <ul><li>動的構成変更技術の研究・開発</li><li>方式① インフラ動的構成変更</li><li>方式② AP実行制御</li></ul>                                                            | 自動設計・構成技<br>術を拡張<br>(70%)                     |

| ※PCIe は、PCI-SIG の登録商標です。                     |                                                      |                                                |                                                            |   |                                                                                                                                       |                                               |

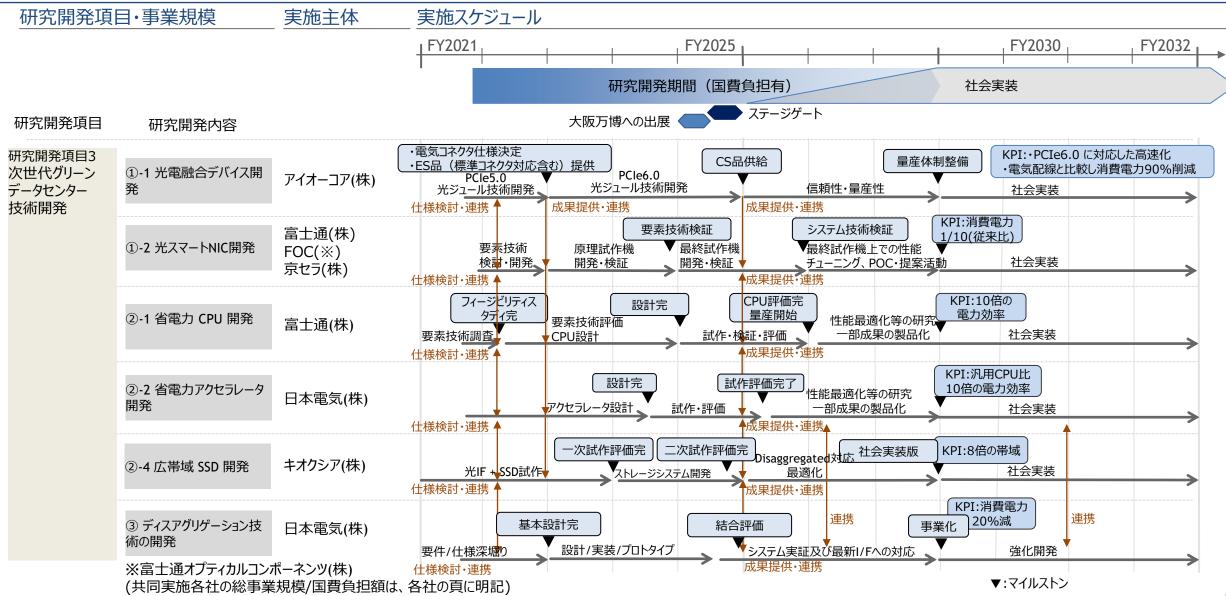

# 2.1 共同実施による研究開発内容/(3) 実施スケジュール

# 複数の研究開発を効率的に連携させるためのスケジュールを計画

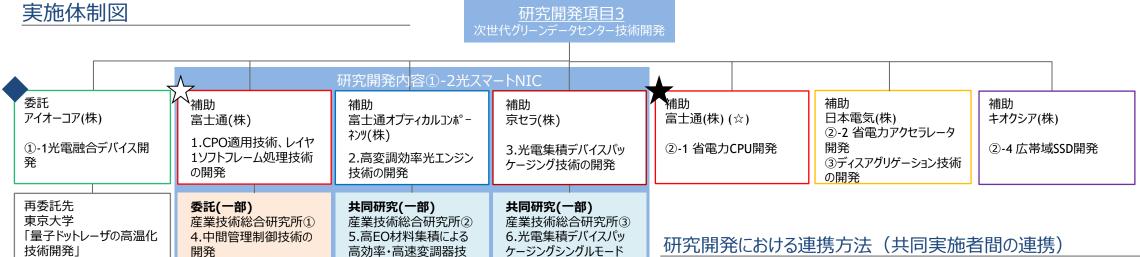

# 2.1 共同実施による研究開発内容/(4)研究開発体制

# 各主体の特長を生かせる研究開発実施体制と役割分担を構築

(共同実施各社の総事業費/国費負担額は、各社の頁に明記)

研究開発項目3 幹事企業

化技術の開発

- ☆ 研究開発内容①-2とりまとめ企業

- 中小・ベンチャー企業

### 各主体の役割

•研究開発項目3は、アイオーコア(株)、富士通(株)、日本電気(株)、キオクシア(株)、富 士通オプティカルコンポーネンツ(株)、京セラ(株)による共同実施である

術の開発

- •研究開発内容①-1光電融合デバイス開発はアイオーコア(株)が担当し、「量子ドットレー ザの高温化技術の開発」を東京大学に再委託する

- •研究開発内容①-2光スマートNIC開発は、富士通(株)、富士通オプティカルコンポーネン ツ(株)、京セラ(株)の3者が担当する、また一部を産業技術総合研究所が担当する

- ②-1省電力CPU開発は富十通が担当する

- •②-2省電力アクセラレータ開発、③ディスアグリゲーション技術の開発は日本電気(株)が担 当する

- ②-4広帯域SSD開発はキオクシア(株)が担当する

- •共同実施者で開発状況や課題を定期的に共有し、研究計画・目標の見直しなどの 連携を行う

- ①-2光スマートNIC開発に特化した連携として、富士通(株)、富士通オプティカルコン ポーネンツ(株)、京セラ(株)、および産業技術総合研究所で開発状況や課題を定期 的に共有し、研究計画・目標の見直しなどの連携を行う

- これらの連携により、ステージゲート、社会実装に向けて互いに連携し、KPI、及び、アウ トプットの目標達成を目指す

### 共同実施者以外の本プロジェクトにおける他実施者等との連携

- ②-3不揮発メモリ開発は本共同実施に含まれないが、不揮発メモリ開発の実施者と も定期的ミーテイングなどで連携を行う

- 次世代グリーンデータセンター用デバイス・システムに関する協議会を設置し、外部機 関と連携を行う

### 中小・ベンチャー企業の参画

中小・ベンチャー企業であるアイオーコア(株)が参画

# 2.1 共同実施による研究開発内容/(5)技術的優位性

# 国際的な競争の中においても技術等における優位性を保有

#### 研究開発項目 研究開発内容 活用可能な技術等 競合他社に対する優位性・リスク 研究開発項目3 **60** -1 • 25Gbps x 4チャネルの超小型光トランシーバ「光I/Oコ 5x5mm<sup>2</sup>の「光I/Oコア」は世界最小 次世代グリーン 光電融合デバイス開発 ア」をアイオーコア(株)が製品化 • 100℃で動作可能な光モジュールを製造できる企業はアイオーコ 100℃で動作可能な光モジュールの設計・製造技術をア データセンター アのみ 競合他社との価格競争がリスク 技術開発 イオーコア(株)が保有 1 -2 • 国内・北米を中心に展開している最先端光伝送装置の 光スマートNICは従来の光伝送装置、スマートNICに対し、フレキ シビリティ・電力・伝送容量/距離等の指標で優位性を有する 光スマートNIC開発 ハードウェア・ソフトウェア開発技術 大手チップベンダーが類似製品を開発販売することと、実施者が • 上記に適用するFPGA等の論理回路設計技術、ネットワー データセンター市場に十分なフットプリントがないことがリスク クOS、ネットワーク運用ソフトウェアの設計技術を有する 省電カプロセッサ開発技術 • 優位性: Intel CPUに対して、3倍の電力性能を達成 • 優位性:富岳性能4期連続 4冠達成 省電力CPU開発 (Green500 No.1@2019年) ハイエンドプロセッサ開発技術 リスク: 開発技術のQCD目標未達 (富岳4冠、UNIX/メインフレーム製品出荷) 2 -2 ベクトル処理・ベクトルキャッシュ技術 • 高性能ベクトル技術・広帯域ベクトルキャッシュ技術は製品の経 省電力アクセラレータ • AI処理に適用可能なマトリクス演算技術 験より優付 開発 リスクとしてマトリクス演算技術に関してはフォロワーであり、充分な 検討・評価が必要である NVMe<sup>™</sup> SSD 優付性:NANDフラッシュメモリからSSDまで完全内部設計なの 広帯域SSD開発 ストレージ管理ソフトウェア で、最新技術の導入が容易 リスク:変化の激しい「データセンタービジネス」への対応に向けて 製品仕様策定や開発で競合に遅れをとるリスクあり 仮想·物理構成変更技術 • 従来装置の構成変更技術に対する継続的な取り組み ディスアグリゲーション • PF抽象化·設計自動化技術 • 要件から設計・構成を導出する技術に関する研究成果はNEC 優位 技術の開発

# 2.2 省電力CPU開発

# 2.2 省電力CPU開発/(1)研究開発目標

## 研究開発内容

アウトプット目標

②-1. 省電力CPU開発

現行富士通CPU(スーパーコンピュータ「富岳」で使用しているA64FX) に対し10倍の電力効率向上

## 技術ポイント

KPI

省電力回路 設計の研究 開発

省電力回路動作技 術活用により電力削 減 (2028年度)

マイクロアーキ テクチャの研 究開発

マイクロアーキテクチャ の効率化により電力 削減 (2028年度)

CPUパッケー ジ関連技術 の研究開発 CPUパッケージ関連 技術活用により電力 削減 (2028年度)

電力効率 10倍

Armアーキテクチャ上で

稼働するソフトウエア

省電力 **CPU**

# 2.2 省電力CPU開発/(2)研究開発内容

### 研究開発内容 アウトプット目標 現行富士通CPU(スーパーコンピュータ「富岳」で使用しているA64FX) ②-1. 省電力CPU開発 に対し10倍の電力効率向上 技術ポイント KPI設定の考え方 **KPI** 実現可能性 省電力回路動作技 60% 2022年度に回路方式を確立し、2025 省電力回路 術活用により電力削 年度までにTEG\*1による評価、CPUプロト 設計の研究 タイプによる動作確認を完了し、2028年 開発 (2028年度) 度に目標電力削減を達成する マイクロアーキ マイクロアーキテクチャ 2022年度にフィージビリティスタディを完了、 75% 2025年度までに設計、CPUプロトタイプに の効率化により電力 テクチャの研 よる動作確認を完了し、2028年度に目 削減 究開発 (2028年度) 標電力削減を達成する CPUパッケージ関連 CPUパッケー 2022年度に回路方式を確立し、2025 60% 技術活用により電力 年度までにTEG\*による評価、CPUプロト ジ関連技術 削減 タイプによる動作確認を完了し、2028年 の研究開発 (2028年度) 度に目標電力削減を達成する

\*1: TEG(Test Element Group) 要素技術確認用のテストサンプル

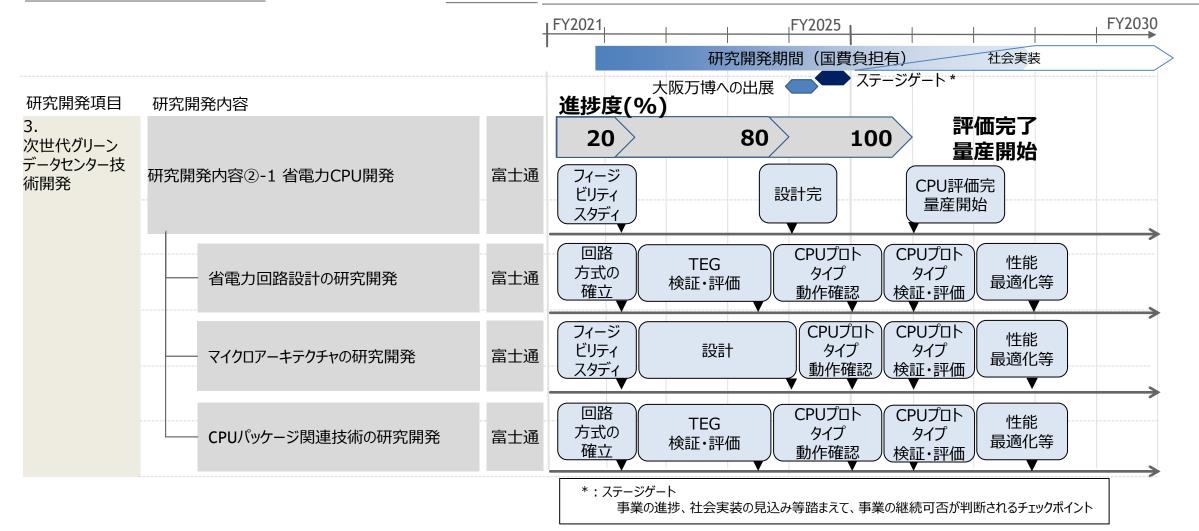

# 2.2 省電力CPU開発/(3) 実施スケジュール

# 複数の研究開発を効率的に連携させるためのスケジュールを計画

- 2025年度までに設計、TEGによる評価、CPUプロトタイプによる動作確認を完了

- 2028年度に目標電力削減を達成する

研究開発項目 事業規模

実施主体 実施スケジュール

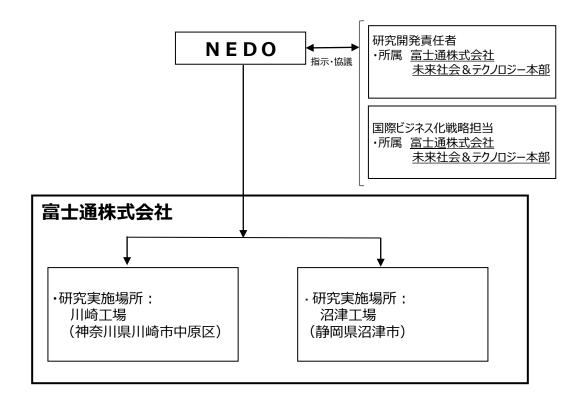

# 2.2 省電力CPU開発/(4)研究開発体制

# 各主体の特長を生かせる省電力回路設計、マイクロアーキテクチャ/CPUパッケージ関連技術の研究開発実施体制と役割分担を構築

## 実施体制図

### 各主体の役割

• ②-1省電力CPU開発は富十通が担当する

### 研究開発における連携方法(共同実施者間の連携)

- ・共同実施者で開発状況や課題を定期的に共有し、研究計画・目標の見直しなどの 連携を行う

- これらの連携により、ステージゲート、社会実装に向けて互いに連携し、KPI、及び、 アウトプットの目標達成を目指す

### 共同実施者以外の本プロジェクトにおける他実施者等との連携

- ②-3不揮発メモリ開発は本共同実施に含まれないが、不揮発メモリ開発の実施者とも定期的ミーテイングなどで連携を行う

- 次世代グリーンデータセンター用デバイス・システムに関する協議会を設置し、外部機 関と連携を行う

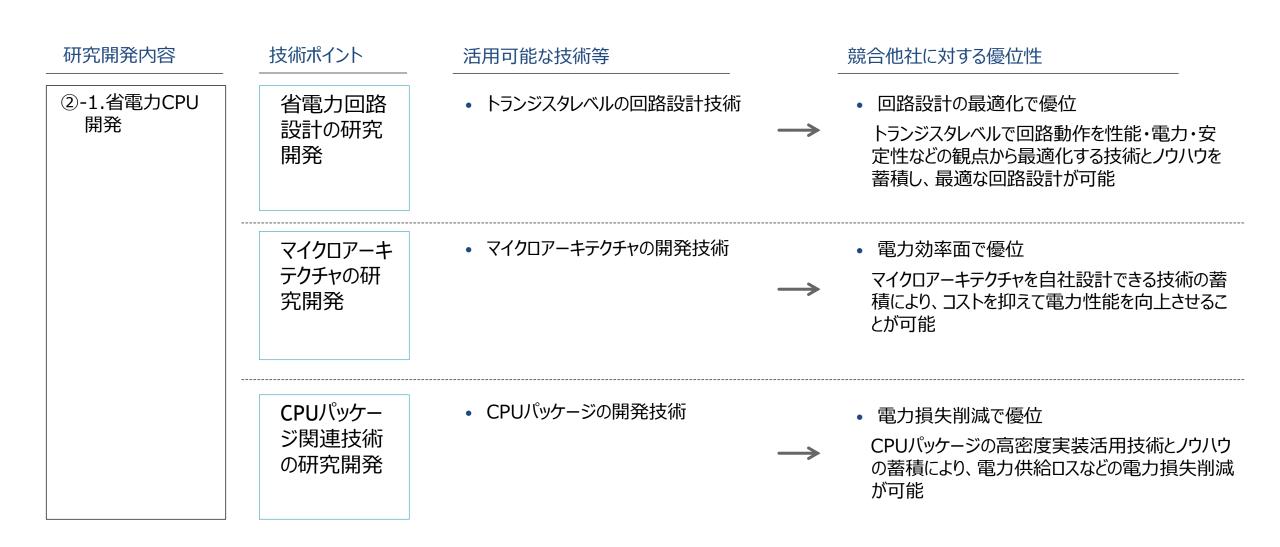

# 2.2 省電力CPU開発/(5)技術的優位性

# 3. イノベーション推進体制

(経営のコミットメントを示すマネジメントシート)

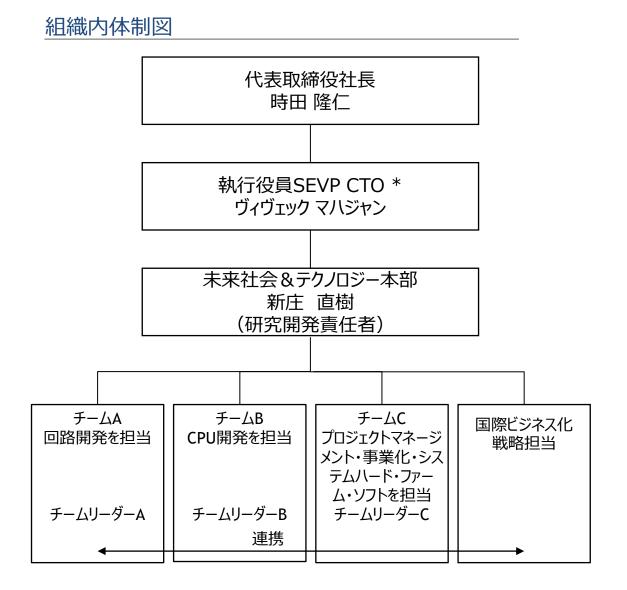

# 3. イノベーション推進体制/(1)組織内の事業推進体制

# 経営者のコミットメントの下に「富岳」開発メンバーによる専門チームを設置

### 組織内の役割分担

### 研究開発責任者

- 富士通 研究開発総責任者

- ヴィヴェック マハジャン 執行役員SEVP CTO \*

- 研究開発責任者

- 新庄 直樹 理事

- 担当チーム

- チームA:回路開発を担当

- チームB: CPU開発を担当

- チームC:プロジェクトマネージメント・事業化・

- システムハード・ファーム・ソフトを担当

- チームリーダー

- A: 最先端半導体における回路開発の実績

- B: UNIX/HPC向けCPU開発の実績

- C:サーバー向けテクノロジー開発の実績

- 国際ビジネス化戦略担当者

- HPC製品企画等の実績

### 部門間の連携方法

- 経営層参加の社内会議を設置し、事業戦略と研究開発状況の確認、方 針判断を行う

- 社内規定に従って研究開発関係者による開発推進会議を定例で開催し、 部門間の連携を図る

\* SEVP: Senior Executive Vice President CTO: Chief Technical Officer

# 3. イノベーション推進体制/(2)マネジメントチェック項目① 経営者等の事業への関与

# 経営者等による本研究開発への関与の方針

### 経営者等による具体的な施策・活動方針

- 経営者等のリーダーシップ

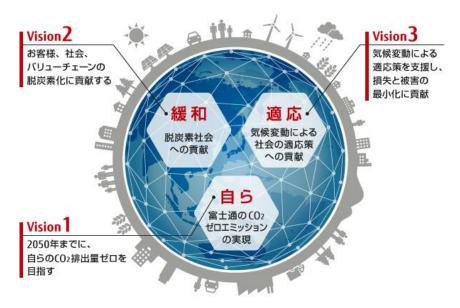

- デジタル革新を支えるテクノロジーやサービスの提供を通じて、脱炭素社会の実現および気候変動への適応に貢献するとともに2050年に自らのCO2排出ゼロエミッションを目指す中長期環境ビジョン「FUJITSU Climate and Energy Vision」を策定し、実現すべき未来の姿を社外に示している。先端技術による革新で、お客様や様々なステークホルダーとエコシステムを形成し、お客様・社会の電力使用の削減やグリーン電力の普及拡大など社会の脱炭素化に貢献し、気候変動の適応に資するサービス・ソリューションを提供することを目指しており、本研究開発もこの中に位置づける

- 富士通は製品やサービス、ビジネスモデルに加えて、業務プロセスや組織、企業文化・風土を変革する全社DXプロジェクトを実施している。産業構造やビジネスモデルの急激な変化に対応するため、デザイン思考やアジャイルなどのフレームワークを活用し、従業員が試行錯誤して自ら変革を続ける組織文化を醸成させている

- 事業のモニタリング・管理

- 経営層はステアリングコミッティにおいて事業進捗状況をモニタリングする。 CPU開発の設計/検証状況、最先端半導体プロセスの状況、装置開発の 状況、パイロットモデルによる先行検証とビジネスプラン検証などの状況にもと づき、市場・競合・テクノロジの外部環境の変化をふまえて、事業の進め方・ 内容に対して意思決定を行う

- 経営会議(またはそれに準ずる会議)において、事業化と研究開発の進捗の 報告を受け、経営判断を行う

### 経営者等の評価・報酬への反映

- 本プロジェクトは、SDGsへの取り組みを経営に組み込むという当社経営方針に沿うものであり、経営者はこの経営方針に照らして業務を執行する

- 役員に適した報酬体系を実現すべく、取締役会の諮問機関として任意に報酬委員会を設置し、以下のとおり、役員報酬の決定プロセスの透明性および客観性ならびに役員報酬体系および水準の妥当性を確保している

- a) 委員は、その過半数を非執行役員で構成し、独立社外取締役を1名 以上確保する

- b) 報酬委員会は、企業価値の持続的向上に対する有効なインセンティブ として機能させることを念頭に、定額報酬の水準と、業績連動報酬の算 定方法を取締役会に答申する

### 担当幹部社員等の評価・報酬への反映

- 担当幹部社員は職責の大きさや重要性により評価されるジョブ型報酬制度 を採用しており、役割や責任、人材要件をジョブプロファイルに定義している。

- 評価においては、パーパスや組織ビジョン実現に向けたインパクト、行動、成長を評価する制度としている。

### 事業の継続性確保の取組

• 事業継続性の確保に向けて、後継者育成(サクセッションプラン)に取り組んでおり、経営層交代時にも中期の経営計画や事業計画をもとに、着実な引継ぎを行う

# 3. イノベーション推進体制/(3)マネジメントチェック項目② 経営戦略における事業の位置づけ

# 経営戦略の中核において本研究開発を位置づけ、広く情報発信

### カーボンニュートラルに向けた全社戦略

- カーボンニュートラルに向けた全社戦略

- 富士通は事業で使用する電力を100%再生可能エネルギーとすることを目指す国際的なイニシアチブ「RE100」に2018年からゴールドメンバーとして加盟しており、再生可能エネルギーの利用を2030年までに40%以上、2050年までには100%にすることを目指している

- 富士通グループの中長期環境ビジョンである、FUJITSU Climate and Energy Visionを策定しており、富士通グループ自らの脱炭素化のノウハウをもとに、お客様、社会に提供することを掲げている

中長期環境ビジョン「FUJITSU Climate and Energy Vision」

## ステークホルダーに対する公表・説明

- 情報開示の方法

- ステークホルダーの期待に応えるべく SDGs への取組みを経営に組み込んでいる

- 経営方針は広報IR活動で開示しており、その中で特にカーボンニュートラルに向けた全社戦略についてはESG(環境・社会・ガバナンス)説明会等で開示している

- ステークホルダーへの説明

- 研究開発、社会実装を進める中で、事業の見通しやリスクを適宜見直し、取引先やサプライヤに対して影響を説明し、共存共栄の関係を築く

- 本研究開発に関する協議会を設置し、各研究開発主体、事業主体、また、省電力デバイスの実用化に必要な様々な周辺サポート事業・技術を担う各研究開発主体、事業主体及びデータセンター事業者等の間において、関係者相互の情報共有、意見交換、共同研究開発の提案を行う

# 3. イノベーション推進体制/(4)マネジメントチェック項目③ 事業推進体制の確保

# 機動的に経営資源を投入し、着実に社会実装まで繋げられる組織体制を整備

## 経営資源の投入方針

- 実施体制の柔軟性の確保

- 内部の開発進捗状況や市場・競合・テクノロジの外部環境の変化をふまえて、必要があれば開発体制や開発手法の見直しを行う。富士通は事業部門起点の人材リソースマネジメントにより、現場への権限委譲と人材の流動化を図っており、必要な人材マネジメントをタイムリーに行う

- 人材・設備・資金の投入方針

- 本研究開発への資金投入を全社戦略に沿った成長投資と位置づけ、 投資を継続的に実施する

- 富岳システムの開発を行ったCPU、装置、ファームウェア、ソフトウェアの 技術者を中心に開発体制を構築する

- 社会実装に向けて、販路の拡大や、パートナーとの更なる連携を実現するため、サーバ事業の経験者を中心に体制を構築する

## 人材の育成

- 若手人材の育成

- 高性能・省電力CPU設計技術、装置設計技術、並列技術・並列分 散処理アプリ開発技術などについて、将来を担う若手人材に継承する

- IOWN Global ForumやOpen Compute Projectなどのオープンコミュニティへの若手の参加を奨励し、幅広い知見を持った人材の育成と、 社外との共同体制を確立を図る

### 社会実装に繋げる組織体制

- コデザイン

- パイロットモデルとしてサービス実証環境を構築。アプリケーションからCPU 仕様へのフィードバック(コデザイン)を行う体制を整備

# 4. その他

# 4. その他/(1) 想定されるリスク要因と対処方針

リスクに対して十分な対策を講じるが、技術的、経済的、その他要因により、事業継続困難な事態に陥った場合には事業中止も検討します

### 研究開発(技術)におけるリスクと対応

- 競合他社の研究開発が想定以上に早く、本研究開発の課題が解消、もしくは陳腐化するリスク

- → 国際学会や国際標準化会議等で競合他社を 含めた技術動向を定期的に確認し、常に先に 行く技術開発の推進、柔軟な計画見直し等を 実施

- 開発技術のQCD目標未達、もしくは採用技術や 採用部品の技術進歩遅延等による競争力低下 のリスク

- → 技術開発のマイルストン毎に、達成度の確認と 競争力の分析を実施する。

- → 分析結果に応じて代替手段への切り替えや追加技術開発、採用技術や採用部品の変更、 投資の方針を判断し、開発に展開

### 社会実装(経済社会)におけるリスクと対応

- ユースケースの想定誤りや市場動向の変化などにより、社会実装前にビジネスモデルが成り立たなくなるリスク

- → 社内サービス事業との連携やIOWN GF等の外 部情報によって、ユースケースを把握

- → 国際学会・標準化会議等を通じて積極的な技術 交換等を実施し、自らターゲット市場の創出等を 実施

- 長期間のプロジェクトであるため、予測不能な市場動向の変化が発生するリスク

- → 定期的に市場動向を確認し、環境変化に柔軟に 対応するための計画変更等を実施

### その他(自然災害等)のリスクと対応

- 未知の感染症拡大により部品供給はじめサプライチェーン停滞によるリスク

- → 研究開発に使用する部品のマルチベンダー化 推進、及び、市場流通品への置き換えが可能 となる部品選定等を実施

- 大規模地震、台風等の自然災害によって研究開発データ破損や拠点被災等が生じ、開発や製造が停滞するリスク

- → テレワーク環境下での開発取り組みを継続し、 勤務地に依存しない開発環境を維持

- → 研究開発データは国内複数地域に自動バック アップ、拠点も国内複数地域に確保

### 事業中止の判断基準:

- 競合他社が先んじて最先端技術を開発し、本研究開発課題の解消、もしくは、本研究開発技術が陳腐化した場合

- 市場動向の変化などにより計画していたビジネスモデルが成り立たたなくなった場合

- 強力な経済制裁などが発動され、部品供給が滞ることで研究開発の実行が困難になった場合

- 自然災害等の発生により、研究開発拠点や試作・製品製造拠点の大規模被災により復旧困難になった場合

- その他、技術的、経済的、その他要因であって通常必要と認められる注意や予防方法を尽くしてもなお防止し得ない要因により事業継続困難な事態に陥った場合