# 事業戦略ビジョン

実施プロジェクト名: 次世代デジタルインフラの構築プロジェクト

【研究開発項目3】次世代グリーンデータセンター技術開発

研究開発内容②光に適合したチップ等の高性能化・省エネ化技術の開発/省電力アクセラレータ開発

実施者名 : 日本電気株式会社 : 代表名:代表取締役執行役員社長 森田 隆之

| 共同実施者 | : 富士通株式会社(幹事会社)

アイオーコア株式会社キオクシア株式会社

富士通オプティカルコンポーネンツ株式会社

京セラ株式会社

# 目次

### 1. 事業戦略・事業計画

- (1) 産業構造変化に対する認識

- (2) 市場のセグメント・ターゲット

- (3) 提供価値・ビジネスモデル

- (4) 経営資源・ポジショニング

- (5) 事業計画の全体像

- (6) 研究開発・設備投資・マーケティング計画

- (7) 資金計画

### 2. 研究開発計画

- 2.1 共同実施による研究開発内容

- (1) 研究開発目標

- (2) 研究開発内容

- (3) 実施スケジュール

- (4) 研究開発体制

- (5) 技術的優位性

### 2.2 省電力アクセラレータ開発

- (1) 研究開発目標

- (2) 研究開発内容

- (3) 実施スケジュール

- (4) 研究開発体制

- (5) 技術的優位性

### 3. イノベーション推進体制(経営のコミットメントを示すマネジメントシート)

- (1) 組織内の事業推進体制

- (2) マネジメントチェック項目① 経営者等の事業への関与

- (3) マネジメントチェック項目② 経営戦略における事業の位置づけ

- (4) マネジメントチェック項目③ 事業推進体制の確保

### 4. その他

(1) 想定されるリスク要因と対処方針

# 1. 事業戦略・事業計画

## 1. 事業戦略・事業計画/(1)産業構造変化に対する認識

# 高速計算への需要は急増・多様化、性能電力効率の良いアクセラレータがデータセンターのグリーン化に大きく貢献

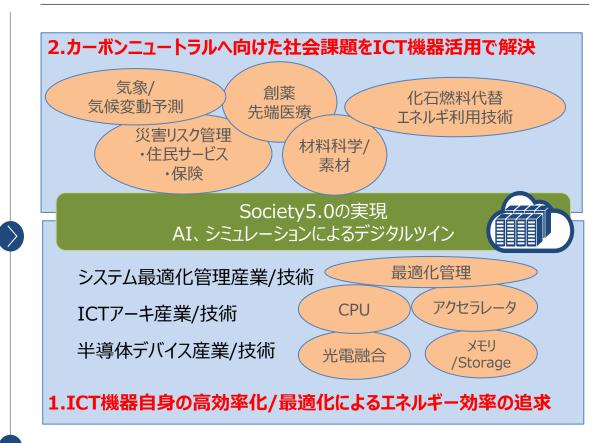

### カーボンニュートラルを踏まえたマクロトレンド認識

#### (社会面)

- 多くの社会課題の解決/低減にデジタル技術が活用され、さらにデジタルトランスフォーメーション(DX)により 産業が繋がり効率向上や新産業の誕生が期待されている

- 一方で、デジタル技術の進展は消費電力の増加を誘引し、データが集積されるデータセンター(DC)の電力増大はカーボンニュートラル(CN)に対する大きな障壁となってきている

#### (経済面)

- CNの実現に対し、ESG投資\*1)など経済社会的な活動が活発化される中、それらの多くの解決にはデジタル技術が活用されているが、そのデジタル技術そのもののコスト削減、性能向上、低消費電力化が求められている

- 複雑化するICTのハードウェア(HW)、ソフトウェア(SW)の利用・管理の効率化のためクラウドDCの活用が 急速に進展している

- IoT、ビッグデータ、人工知能(AI)の高度/高速な計算処理が求められてきており、特定の演算を得意とするアクセラレータの導入によるコスト低減、消費電力削減への期待が寄せられている

#### (政策面)

- これまでも様々な消費電力削減の革新的HW/SW技術が産官学連携により開発されてきたが、急激に増加するデータの処理に、さらなる技術革新が求められている

- 経済安全保障では、半導体の供給問題が深刻となる中で、日本のデータを守る国内DC(地域DCなど)の整備が促進されている

#### (技術面)

- CNの実現に対し2点の観点での取組みが求められる

- 1.DCを構成するICT機器自身の高効率化/最適化によるエネルギー効率の追求

- 2.CNの実現に向けた社会課題をDC/ICT機器活用したアプリケーションで解決

- 半導体製造技術進展の鈍化により、汎用CPUだけでは省電力化は難しく、光電技術により他のICT機器と接続されたアクセラレータの開発、多様なアクセラレータを管理するシステムSWの融合が必要となってきている

#### ● 市場機会:

DCの様々な処理をより高速に低消費電力で計算できる高性能サーバ市場のうち、2027年には約30%でアクセラレータが活用されると推定している

● 社会・顧客・国民等への貢献: カーボンニュートラルへ向けたデジタル技術とそれを活用した社会を支え、Society5.0の実現による 安心・安全でより便利な社会を実現する カーボンニュートラル社会における産業アーキテクチャ

#### 当該変化に対する経営ビジョン:

「未来の共感を創る」というコーポレートビジョンの下、中長期の環境目標策定し、未来に向けて、自社の環境負荷やリスクの継続的な低減と事業を通じた貢献の拡大に取り組んでいます

こうしたビジョン/目標にもとづき、調達/製品としての環境負荷低減はもちろん、"地球と共生する" NECの環境ソリューションとしてDXで環境課題を解決するソリューションの提供を開始しています

\*1)ESG投資:従来の財務情報だけでなく、環境(Environment)・社会(Social)・ガバナンス(Governance)要素も考慮した投資

# 1. 事業戦略・事業計画/(2) 市場のセグメント・ターゲット

高性能サーバ市場全体の30%

高速計算需要を担う高性能サーバ市場で、特にアクセラレータ等で高性能・低消費電力を求める領域をターゲットと想定

### セグメント分析

- 高性能サーバ市場のうち、アクセラレータ搭載サーバ市場は、約30%と推定

- アプリケーション特性に最適な高速性と高い電力効率を求める処理では専用アクセラレータ搭載(GPU等)によるヘテロ・コンピューティング化が進展

#### がアクセラレータ市場と推定 ΑI AI領域のセグメンテーションとニーズ テキスト分析 **HPC** 災害 統計的 (分類) ルート 予測 機械 最適化 需要予測 学習 故障予測 都市計画 レコメンド 老朽化診断 製造プロセス 最適化 医療診断 検品 (画像認識) 監視カメラ 学習 自動運転 解析 自動翻訳 公共 企業 社会 高性能サーバ市場(全体)

### ターゲットの概要

### 市場概要と目標とするシェア・時期

市場投入を開始する2027年におけるアクセラレータ利用市場で、AI領域と高性能計算(HPC)領域の比は1:3と予測

AI領域 :民需経済領域の市場予測、故障予測等の用途 HPC領域:政府系を中心に災害予測、気象・気候予測等の各種数値シミュレー ション用途

### 今後、AI用途を中心にアクセラレータ活用が進展する市場

| 需要家        | 主なプレーヤー                |                                                                              | 想定ニーズ                                                                  |

|------------|------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------|

| 政府系        | 各省庁<br>自治体<br>各国ラボ     | <ul><li>地域・組織を超えた<br/>データの共有</li><li>情報セキュリティ</li><li>公開用のデータトリミング</li></ul> | <ul><li>災害予測</li><li>都市計画</li><li>気象・気候</li><li>各種数値シミュレーション</li></ul> |

| 流通、製造交通、通信 | 国内外<br>上場企業            | <ul><li>・ データ収集</li><li>・ データマイニング</li><li>・ 関連性の解析</li></ul>                | <ul><li> 故障予測</li><li> レコメンド・顧客動向</li><li> 流体/構造解析</li></ul>           |

| 金融         | メガバンク<br>生保・損保<br>海外金融 | <ul><li>個人情報保護</li><li>システム連携</li><li>データの抽出・加工</li><li>判断根拠(説明性)</li></ul>  | <ul><li>不正検知</li><li>市場予測</li></ul>                                    |

# 1. 事業戦略・事業計画/(3) 提供価値・ビジネスモデル

# ベクトルアクセラレータの低消費電力・高性能化によりベクトル得意領域でDCの省電力化に貢献

### 社会・顧客に対する提供価値

- 演算性能あたりの電力削減による グリーンイノベーションの実現

- 大量なデータの一括した処理で演 算性能あたりの省電力性に優れる ベクトルプロセッサに高メモリバンド幅 を実現し、現行汎用CPUサーバの 性能あたりの電力量を大幅に削減

- 気候予測/河川氾濫予測/津波予 測等の予測精度向上により安全安 心な社会の実現に貢献

- ・電力要件に応じたスケーラブルなアク セラレータ構成による低消費電力化

- アプリケーションプログラム特性に応じ て必要となるチップレットのみ使用す ることで低消費電力化

- 将来的には、更なる低消費電力化を 加速。組込み領域等にも適用領域を 広げ、デジタルツインの実現に貢献

ビジネスモデルの概要(製品、サービス、価値提供・収益化の方法)と研究開発計画の関係性

## 事業戦略(次世代グリーンDC)

現在

HPC用ベクトル型アクセラレータ

●グローバルに国研を中心にシミュ

●大データ行列計算は機械学習演

算に適していることを実証、CPUの

レータ用HPCに採用

数十倍の速さ

- ▶超低消費電力、高性能アクセラレータとしてDC等に普及

- ▶産業・公共・社会に用いられる高度な分析アプリも併せて提供

次世代 本研究 グリーンDC

### DC用ベクトル型アクセラレータ

- ◆人工知能の演算性能を高めながら、 ラック搭載 省電力化設計を駆使し消費電力低減

- ●科学技術計算から産業用途分析計算 などの用途に合わせてチップ自身の構成を 最適化できる構造を開発

### 将来

# Society 5.0実現

### 将来事業戦略(Society5.0の実現)

- ▶様々な規模のコンピュータに広くアクセラ レータを展開

- ▶高度な気象・環境予測とリアルタイムデー タに基づく適用制御などのデジタルツイン型 サービスの提供

# デジタルツイン の進化

(b) =00 (b) =00 (c) =00

適用領域の拡大

# 1. 事業戦略・事業計画/(4)経営資源・ポジショニング

スーパーコンピュータ開発で培ったベクトル技術とその顧客基盤とのリレーションを強みに、アクセラレータの高性能・低消費 電力化とディスアグリゲーション開発を推進し、将来はNECが強みを持つ社会インフラ・公共機関の高度化に貢献

### 自社の強み、弱み(経営資源)

### ターゲットに対する提供価値

- ベクトルアクセラレータ、および、ディスアグリゲーション 技術による高性能・低消費電力化

- ベクトルアクセラレータ向けソフトウェア開発キット (SDK)による簡易なプログラム開発・実行環境

### 自社の強み

- 最先端のベクトルアクセラレータ開発力

- 低消費電力・高性能を実現する開発力

- 国内外のベクトルの顧客基盤

- NEC全体として持つ社会インフラや公共機関等の 顧客基盤

### 自社の弱み及び対応

弱み:現在のプログラムは多岐に渡り、ベクトルアーキテク チャだけでは全てのプログラムの特性をカバー什切 れない

対応:30年を超える開発で培ったベクトル技術を生かし ながら、様々な計算資源(CPU、GPUなど)と組 合わせるディスアグリゲーション技術を提供

#### 他社に対する比較優位性 ユーザ・パートナー 技術 顧客基盤 その他経営資源 リレーション • 高性能計算(HPC)向けの • HPC系の国内、欧州 •国内外のアカデミア/ •業務システム構築SI力 自社 を中心とした海外の大 ベクトルアクセラレータ技術 企業のHPC系の研 • AI活用技術 ベクトル処理用ソフトウェア 国内サービス網 学・国研DC・気象サイ 究者とのリレーション 開発キット(SDK) • 海外拠点 ベクトル処理に特化 • AI/HPC向けの省電力・ •低消費電力/高性能 • AI/HPC開発者や 社会インフラ、通信キャリア 高性能なベクトルアクセラ な処理を必要とする ベンダとのコミュニ 等の顧客基盤 レータ技術 DC(AI/HPC) ティ・学会との連携 ディスアグリゲーションの研 •様々な演算・処理に対し • 大規模データの • ディスアグリゲーション 究開発 CPU/GPU/ベクトル等を AI/HPC処理が進む を実現するパート (本研究別テーマ) 最適にかつシームレスに連 金融/流通/製造/通 ナーとのリレーション 携するディスアグリゲーション 信が利用するDC を実現 PC/サーバベンダ

他社CPU ベンダー

- 汎用性の高いCPU、プロ グラム環境

- 厖大なプログラム資産を活 かす後方互換アーキテク

- 深層学習のアクセラレータゲーム・グラフィックス

組込機器ベンダ

- AIサービス企業

- ニューラルネット処理に特化・深層学習用途の DC企業

- チップサプライヤとし、 てPC/サーバベンダ 中心のリレーション

- 膨大な研究開発投資 カ、WWに構築されたサプ ライチェーン網

- アクセラレータ・サプ ライヤとしてアプリベ ンダやサービスベンダ 中心のリレーション

- •膨大な研究開発投資力, ファブレス、アクセラレータ 特化

他社 アクセラレータ ベンダー

# 1. 事業戦略・事業計画/(5) 事業計画の全体像

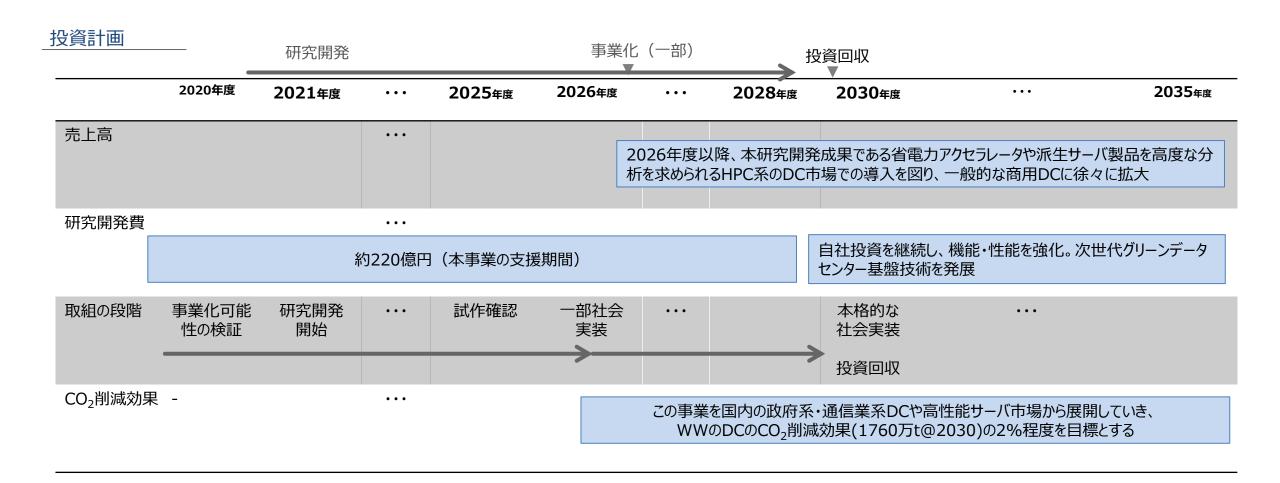

# 5年間の研究開発の後、2026年度以降から成果を事業化、2029年度頃の投資回収を想定

# 1. 事業戦略・事業計画/(6)研究開発・設備投資・マーケティング計画

アプリケーション分析や半導体プロセス特性を考慮した高性能・低消費電力のベクトルアクセラレータを開発・試作し、共同 実施社と連携した光接続の確認を行うとともに、適用市場拡大に向けたマーケティングを展開

### 研究開発·実証

### 設備投資

### マーケティング

### 取組方針

国際競争

上の

優位性

- •実アプリケーションを用いて、設計段階のアクセラ レータLSIの機能・動作エミュレーションを活用する ことにより、高性能化するべき処理や低消費電力 となるべき設計法を確立

- •LSI製造は最適な社外ベンダーを選択。LSIを製 ・大規模DCへの導入を目指し、リファレンスシステム 品に搭載する生産設備は既存設備を最大限活

- を獲得に加えて、自社DCでの実績蓄積して、中小 規模DC市場へ展開

- •ベクトルアクセラレータの試作と共同実施社との接 続評価を実施し、効果を実証

- コモデティ部品は、WWに調達。ベクトル・アクセラ レータに特化して、品質・性能の担保が必要な部 材は、国内ベンダー中心に調達予定

- ベクトルアクセラレータ、ディスアグリゲーション技術を アカデミア、パートナー等に広く展開し、エコシステム を構築

- ・ディスアグリゲーション制御対象として電源制御など・事業化後、生産量の増加に伴い、製造設備の増 の連携を行う

- 強・更新を順次実施

ハードウェア/ソフトウェアでのベクトル技術

- 30年以上のベクトルプロセッサ開発で培った。

- ●事業拡大(生産量増)に伴い、部品コスト低減、●HPC系の国内および欧州を中心とした海外の大 生産効率改善を図り、国際競争力向上に努める

- 弊社だけがもつベクトルアクセラレータとディスアグリ ゲーション技術による性能・省電力優位性

- •ISO9001認証取得の品質管理の下、サーバ/メ インフレーム/スパコンまで多様な製品を高品質で 牛産してきた実績

- 共同実施社と連携した、将来の基盤技術となる 光電融合・光インタフェースによる他装置との接続 技術

学・国立研究機関DC・気象サイトをはじめ、北米 / アジア / 中南米などの自社海外拠点を経由し、 海外展開を図る

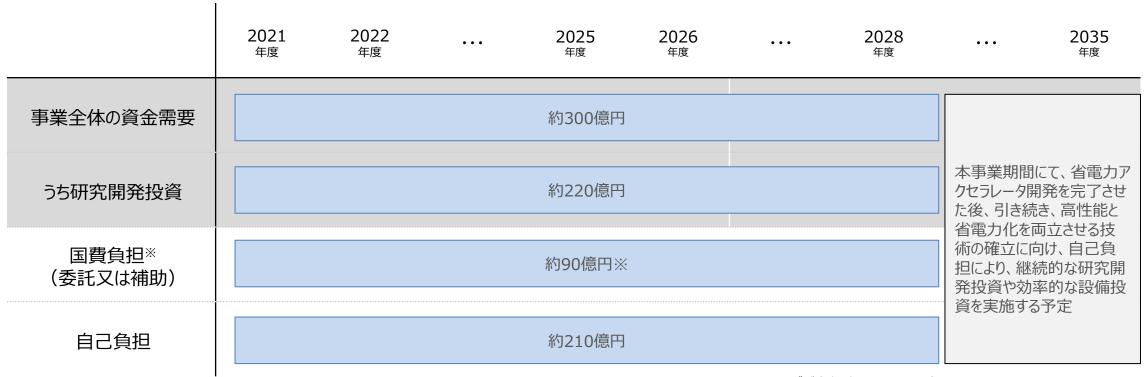

# 1. 事業戦略・事業計画/(7)資金計画

# 国の支援に加えて、200億円規模の自己負担を予定

### 資金調達方針

自己負担分は、すべて自己資金より充当する

※インセンティブが全額支払われた場合

# 2. 研究開発計画

# 2.1 共同実施による研究開発内容

# 2.1 共同実施による研究開発内容/(1)研究開発目標

# DCの省力化40%以上というアウトプット目標を達成するために必要な複数のKPIを設定

#### 研究開発項目 アウトプット目標 2030 年までに、研究開発開始時点で普及しているデータセンターと比較して 40%以上の省エネ 【研究開発項目3】 化を実現 次世代グリーンデータセンター技術開発 研究開発内容 KPI設定の考え方 **KPI** ・PCIe6.0 に対応した光トランシーバを開発 DCの4.4%の電力消費が電気配線であり、光配線化することで配線に 光電融合デバイス開発 ・チップ間接続の消費電力を電気配線と比較して 関わる電力を1/10までに削減する 90%削減 1 -2 ・ビットあたり消費電力を従来比で1/10へ削減 現行の光伝送装置の消費電力から、CPO技術適用とレイヤ1ソフトフ 光スマートNIC開発 レーム処理技術適用によりビット当たりの消費電力1/10を実現する 2 -1 ・現行自社CPUに対し10倍の電力効率向上 DCの省力化40%以上を達成するためには、消費電力占有率が最も 省電力CPU開発 高いCPUの電力効率を10倍に改善する高い目標設定が必要 ・現行汎用CPU比10倍の電力効率、メモリ帯域 -2 アクセラレータで利用するアプリで現行汎用CPU比10倍の電力効率。複 省電力アクセラレータ開発 5TB/s以上 数チップレット(複数HBM搭載)の構成で5TB/s以上のメモリ帯域を 実現する ・連続リード性能(或いは帯域)を現行(PCIe® Gen.3 サーバーの電力効率を向上させるためにはストレージの広帯域化が必要。 広帯域 SSD 開発 世代相当)から8倍にする 2028年にストレージシステムとして128GB/sを達成する ・制御対象機器の利用効率の最適化により、制御 ワークロード特性に対応した動的構成変更により、最適なリソースを割り ディスアグリーゲーション技術の開発 対象機器を制御しない場合と比較して消費電力 当て、不要部分の電力を削減することで消費電力を20%程度改善 20%の削減

※PCIe は、PCI-SIG の登録商標です。

# 2.1 共同実施による研究開発内容/(2)研究開発内容

# 各KPIの目標達成に必要な解決方法を研究開発

|                                              | KPI                                                  | 現状                                           | 達成レベル                                                         | ı | 解決方法                                                                                                                                  | 実現可能性 (成功確率)                                  |  |

|----------------------------------------------|------------------------------------------------------|----------------------------------------------|---------------------------------------------------------------|---|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| 1 -1<br>光電融合デバイス開発                           | ・PCIe6.0 に対応<br>・電気配線と比較して<br>電力 90%減                | 電子回路等の要素技術(TRL4)                             | 信頼性・量産性を<br>満足した製品レベ<br><b>→</b> ル(TRL9)                      |   | <ul><li>低損失シリコンフォトニクス回路技術</li><li>① リニアリティの高い光素子による高速PCle6.0</li><li>(32GBau,PAM4)</li><li>② 電子回路のCDRが不要となり低電力化</li></ul>             | 低損失シリコンフォト<br>ニクス回路の適用に<br>より高い実現可能性<br>(90%) |  |

| 1 -2<br>光スマートNIC開発                           | ビットあたり消費電力<br>を従来比で1/10へ削<br>減                       | レイヤ1ソフトフ<br>レーム処理技術<br>は研究開発段<br>階(TRL2)     | 製品一歩手前の<br>プロトタイプ機の<br>➤ 完成(TRL6)                             |   | <ul> <li>システム、部品、集積の3要素技術を集結</li> <li>システム: CPO適用技術、レイヤ1ソフトフレーム処理技術</li> <li>部品:高変調効率光エンジン技術</li> <li>集積:光電集積デバイスパッケージング技術</li> </ul> | 世界最高水準の技<br>術を持つ3社の集結<br>で成功確率は高い<br>(80%)    |  |

| <sup>2</sup> -1<br>省電力 CPU 開発                | 現行自社CPUに対し<br>10倍の電力効率向<br>上                         | 一部の技術開発項目において、原理確認段階 (TRL1)                  | 技術開発の検<br>証・評価と、後半<br><b>&gt;</b> の実証システムに<br>向けた試作<br>(TRL4) |   | <ul><li>富岳で採用した省電力回路設計技術を進化</li><li>省電力につながる新しいデバイスの取り込みや、テクノロジを開発</li></ul>                                                          | 原理確認段階の開発項目がある為<br>(60%)                      |  |

| <ul><li>2 -2<br/>省電力アクセラレータ<br/>開発</li></ul> | 現行汎用CPU比10<br>倍の電力効率、メモリ<br>帯域5TB/s以上                | 汎用CPU比5倍<br>の電力効率、メ<br>モリ帯 1.5TB/s<br>(TRL4) | 汎用CPU比10<br>倍以上の電力効<br>➤ 率、メモリ帯域<br>5TB/s以上<br>(TRL5)         |   | <ul><li>ベクトル・アーキテクチャの機能強化やチップ内部のマイクロ・アーキテクチャ改良による電力効率向上</li><li>チップレット設計によるメモリ帯域5TB/s 構成の実現</li></ul>                                 | 所望アプリのベンチ<br>マーク電力当たり性<br>能改善<br>(70%)        |  |

| 2 -4<br>広帯域 SSD 開発                           | 連続リード性能(或いは<br>帯域)を現行(PCIe®<br>Gen.3世代相当)から<br>8倍にする | PCIe® Gen3<br>相当(TRL3)                       | PCIe® Gen6<br>相当(TRL7)                                        |   | <ul> <li>光インターフェイスブリッジの最適実装,ディスアグリゲーション対応ストレージ管理SW開発</li> <li>方式① 最適帯域となる管理SW</li> <li>方式② 低電力CPUで管理SW実行</li> </ul>                   | 達成レベルに未達の<br>可能性あり<br>(70%)                   |  |

| 3<br>ディスアグリゲーション<br>技術の開発                    | 効率の最適化により、<br>制御対象機器を制御<br>しない場合と比較して<br>消費電力20%の削減  | (TRL3)                                       | コンポーネント単位のAP要求性<br>・ 能に応じた動的自動構成変更<br>(TRL7)                  |   | <ul><li>動的構成変更技術の研究・開発</li><li>方式① インフラ動的構成変更</li><li>方式② AP実行制御</li></ul>                                                            | 自動設計・構成技<br>術を拡張<br>(70%)                     |  |

| ※PCIe は、PCI-SIG の登録商標です。                     |                                                      |                                              |                                                               |   |                                                                                                                                       |                                               |  |

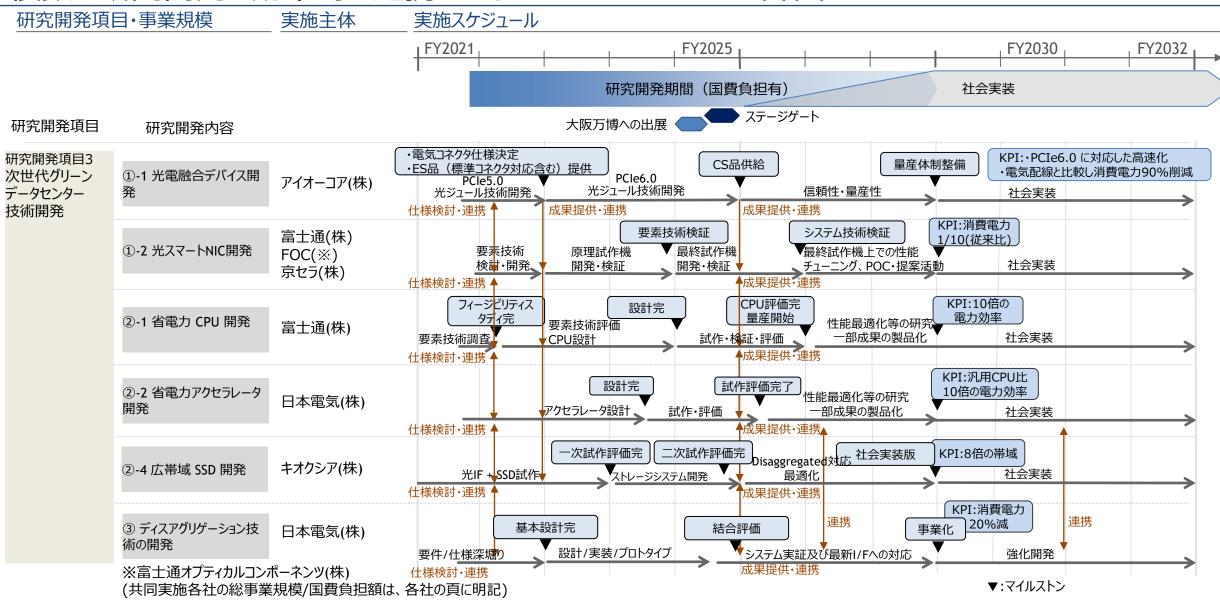

# 2.1 共同実施による研究開発内容/(3) 実施スケジュール

# 複数の研究開発を効率的に連携させるためのスケジュールを計画

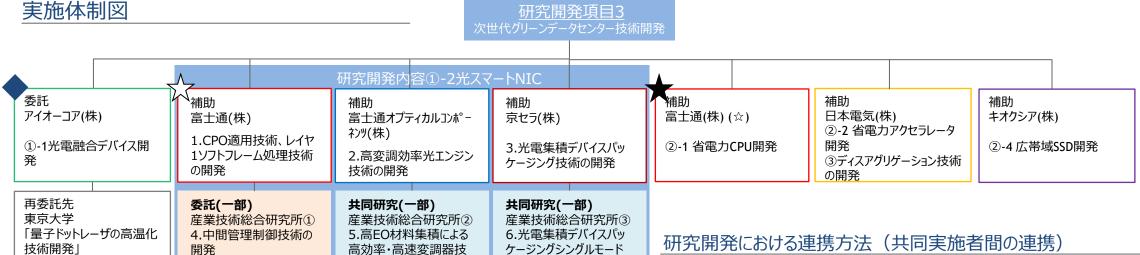

# 2.1 共同実施による研究開発内容/(4)研究開発体制

# 各主体の特長を生かせる研究開発実施体制と役割分担を構築

(共同実施各社の総事業費/国費負担額は、各社の頁に明記)

研究開発項目3 幹事企業

化技術の開発

- ☆ 研究開発内容①-2とりまとめ企業

- 中小・ベンチャー企業

### 各主体の役割

•研究開発項目3は、アイオーコア(株)、富士通(株)、日本電気(株)、キオクシア(株)、富 士通オプティカルコンポーネンツ(株)、京セラ(株)による共同実施である

術の開発

- •研究開発内容①-1光電融合デバイス開発はアイオーコア(株)が担当し、「量子ドットレー ザの高温化技術の開発」を東京大学に再委託する

- •研究開発内容①-2光スマートNIC開発は、富士通(株)、富士通オプティカルコンポーネン ツ(株)、京セラ(株)の3者が担当する、また一部を産業技術総合研究所が担当する

- ②-1省電力CPU開発は富十通が担当する

- •②-2省電力アクセラレータ開発、③ディスアグリゲーション技術の開発は日本電気(株)が担 当する

- ②-4広帯域SSD開発はキオクシア(株)が担当する

- •共同実施者で開発状況や課題を定期的に共有し、研究計画・目標の見直しなどの 連携を行う

- ①-2光スマートNIC開発に特化した連携として、富士通(株)、富士通オプティカルコン ポーネンツ(株)、京セラ(株)、および産業技術総合研究所で開発状況や課題を定期 的に共有し、研究計画・目標の見直しなどの連携を行う

- これらの連携により、ステージゲート、社会実装に向けて互いに連携し、KPI、及び、アウ トプットの目標達成を目指す

### 共同実施者以外の本プロジェクトにおける他実施者等との連携

- ②-3不揮発メモリ開発は本共同実施に含まれないが、不揮発メモリ開発の実施者と も定期的ミーテイングなどで連携を行う

- 次世代グリーンデータセンター用デバイス・システムに関する協議会を設置し、外部機 関と連携を行う

### 中小・ベンチャー企業の参画

中小・ベンチャー企業であるアイオーコア(株)が参画

# 2.1 共同実施による研究開発内容/(5)技術的優位性

# 国際的な競争の中においても技術等における優位性を保有

#### 研究開発項目 研究開発内容 活用可能な技術等 競合他社に対する優位性・リスク 研究開発項目3 **60** -1 • 25Gbps x 4チャネルの超小型光トランシーバ「光I/Oコ 5x5mm<sup>2</sup>の「光I/Oコア」は世界最小 次世代グリーン 光電融合デバイス開発 ア」をアイオーコア(株)が製品化 • 100℃で動作可能な光モジュールを製造できる企業はアイオーコ 100℃で動作可能な光モジュールの設計・製造技術をア データセンター アのみ 競合他社との価格競争がリスク 技術開発 イオーコア(株)が保有 1 -2 • 国内・北米を中心に展開している最先端光伝送装置の 光スマートNICは従来の光伝送装置、スマートNICに対し、フレキ シビリティ・電力・伝送容量/距離等の指標で優位性を有する 光スマートNIC開発 ハードウェア・ソフトウェア開発技術 大手チップベンダーが類似製品を開発販売することと、実施者が • 上記に適用するFPGA等の論理回路設計技術、ネットワー データセンター市場に十分なフットプリントがないことがリスク クOS、ネットワーク運用ソフトウェアの設計技術を有する 省電カプロセッサ開発技術 • 優位性: Intel CPUに対して、3倍の電力性能を達成 • 優位性:富岳性能4期連続 4冠達成 省電力CPU開発 (Green500 No.1@2019年) リスク: 開発技術のQCD目標未達 ハイエンドプロセッサ開発技術 (富岳4冠、UNIX/メインフレーム製品出荷) 2 -2 ベクトル処理・ベクトルキャッシュ技術 • 高性能ベクトル技術・広帯域ベクトルキャッシュ技術は製品の経 省電力アクセラレータ • AI処理に適用可能なマトリクス演算技術 験より優付 開発 リスクとしてマトリクス演算技術に関してはフォロワーであり、充分な 検討・評価が必要である NVMe<sup>™</sup> SSD 優付性:NANDフラッシュメモリからSSDまで完全内部設計なの 広帯域SSD開発 ストレージ管理ソフトウェア で、最新技術の導入が容易 リスク:変化の激しい「データセンタービジネス」への対応に向けて 製品仕様策定や開発で競合に遅れをとるリスクあり 仮想·物理構成変更技術 • 従来装置の構成変更技術に対する継続的な取り組み ディスアグリゲーション • PF抽象化·設計自動化技術 • 要件から設計・構成を導出する技術に関する研究成果はNEC 優位 技術の開発

# 2.2 省電力アクセラレータ開発

# 2.2 省電力アクセラレータ開発/(1)研究開発目標

# 電力効率10倍というアウトプット目標を達成するために必要な複数のKPIを設定

### 研究開発内容

省電力アクセラレータ開発 Scalable Vector Accelerator(SVA)

### アウトプット目標

- 1. アクセラレータで利用するアプリで、現行汎用CPU比10倍の電力効率

- 2. メモリ帯域5TB/s以上のベクトルアクセラレータ開発

### 研究開発項目

1 アーキテクチャ強化による 電力効率向上

### **KPI**

電力当たりのベンチマーク性能

### KPI設定の考え方

現行汎用CPUのベンチマーク電力性能に対する期待 倍数を設定する

2 所望とするメモリ帯域の実現

メモリ帯域と電力あたりメモリ帯域

チップレットをいくつか組み合わせた構成における所望のメモリ帯域を設定する

3 次世代標準インタフェース の実装と光接続の実証

理論IO帯域の性能値 共同実施社間で合意した次世代標準インターフェースを実装 共同実施目標の広帯域な次世代標準インタフェース 規格を実装。必要なレーン数とport数を実装し、他 コンポーネントとの理論IO帯域として期待されるイン ターフェース性能値を設定する

4 Armプロセッサとアクセラ レータ連携制御ソフト ベンチマーク測定を試作機で実行可能なこと。Core性能、IO帯域、メモリ帯域を試作機で測定可能なこと

ベンチマークや性能測定が可能であれば、制御ソフト およびコンパイラ、計算ライブラリの実現性を検証でき たことになる

# 2.2 省電力アクセラレータ開発/(2)研究開発内容(1/3)

# 各KPIの目標達成に必要な解決方法を研究開発

|                                   | KPI                                                 | 現状                                                              | 達成レベル                                                          | 解決方法                                       | 実現可能性<br>(成功確率)                             |

|-----------------------------------|-----------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------|---------------------------------------------|

| 1 アーキテクチャ強化による電力効率向上              | 電力当たりのベンチマーク性能                                      | 電力当たり性能<br>のGF/W値<br>(TRL4) ◆                                   | 現状規定倍以<br>上<br><b>→</b> (TRL5)                                 | ベクトルアーキテクチャへの取り込みを検討り                      | ンチマーク電力当た<br>生能改善<br>0%)                    |

| 2 所望とするメモリ帯域の実現                   | メモリ帯域と電力あ<br>たりメモリ帯域                                | メモリ帯域の<br>TB/s値<br>電力あたりメモリ◆<br>帯域のGB/s/W<br>値<br>(TRL4)        | 現状の規定倍<br>以上<br>→ (TRL5)                                       | - チップレット間データ通信帯域向上 上 低電力のための演算ブロック最適配置 ・ 戸 | 所望のメモリ帯域以<br>(80%)<br>所望の電力当たりメ<br>J帯域(60%) |

| 3 次世代標準インタ<br>フェースの実装と光<br>接続の実証  | 理論IO帯域の性能値<br>共同実施社間で合意した次世代標準インターフェースを実装           | IO帯域のGB/s<br>値<br>(TRL4) ◆                                      | 現状の規定倍以<br>上かつ共同実施<br>社間で合意した<br>次世代標準インタ<br>フェースを実装<br>(TRL5) | 様、次世代標準インターフェースを実装し、代                      | 望のIO帯域と次世<br>標準インターフェー<br>の実装 ( 80%)        |

| 4 Armプロセッサとア<br>クセラレータ連携制<br>御ソフト | ベンチマーク測定を試作機で実行可能なこと。Core性能、IO帯域、メモリ帯域を試作機で測定可能なこと。 | Armエミュレータ<br>と、アクセラレータ<br>エミュレータによる <b>◆</b><br>実現性検証<br>(TRL4) | Armプロセッサと<br>アクセラレータ実<br>→機による検証<br>(TRL5)                     | <b>- カーフー コンパン コーニー ケケー ノデーロ</b>           | 現可能性高<br>80%)                               |

# 2.2 省電力アクセラレータ開発/(2)研究開発内容(2/3)

# 省電力アクセラレータ(スケーラブル・ベクトル・アクセラレータ(SVA))研究開発概要

概況: 半導体技術の進展が鈍化する昨今において、汎用CPUのみで構成されるデータセンター(DC)では多種多様化するワークロードに対して省電力化の達成は難しく、特定領域のワークロードを高い電力効率で実行するアクセラレータが今後益々求められる

目標: NECのベクトルアクセラレータは、AI分野の中でも高いシェア・ニーズを有する「統計的機械学習」の領域において非常に高い電力効率を発揮し、これを次世代DCに組み込むための研究開発を行う。このベクトルアクセラレータは次世代グリーンデータセンター(GDC)の名に相応しい、「現行CPU比10倍の電力効率」および「メモリ帯域5TB/s以上の実現」を目標とする

研究①/②:この達成のために、現行製品から更なる電力効率向上にむけたアーキテクチャ強化を図る他、**最先端のチップレット設計**を採用し、最先端メモリ であるHigh Bandwidth Memory(HBM)のパッケージ上への多数個搭載を図る

研究③:また、次世代GDCを構成する省電力CPU・光スマートNIC・広帯域SSD等の異種デバイス間は次世代標準インタフェースを採用した光接続を行う

研究④:ArmアーキテクチャのホストCPUへの対応として、Armプロセッサ~ベクトルアクセラレータ間の連携を行うための制御ソフトの開発も行う

事業化:将来の社会実装では、次世代GDC向けに加え、小型・低消費電力が要求されるエッジ領域でのベクトルアクセラレータ活用も想定し、チップレットおよびそのパッケージング技術を活用したスケーラブル・ベクトル・アクセラレータ(SVA)を製品化・事業化することでSociety5.0の実現に貢献する

### 研究開発項目

- 1 アーキテクチャ強化による電力効率向上

- ② 所望とするメモリ帯域の実現

- ③ 次世代標準インタフェースの実装と光接続の実証

- 4 Armプロセッサとアクセラレータ連携制御ソフト

# 2.2 省電力アクセラレータ開発/(2)研究開発内容(3/3)

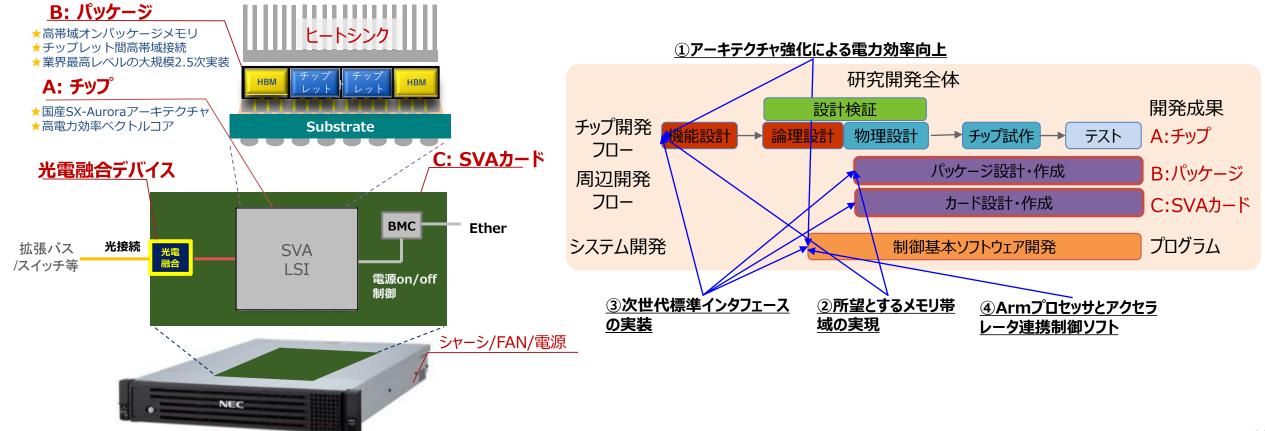

# SVA試作イメージ・研究開発全体と研究開発項目の関係

# SVAのLSIを開発し、光電融合デバイスを搭載したカードで、省電力を検証する

### 試作イメージ

最先端LSIプロセス製造されたA:チップを、業界最高レベルの実装技術により多数個の最先端メモリと同一B:パッケージ上に実装し、光電融合デバイスとC:SVAカード上で接続した上で、これら一式をシャーシに格納する

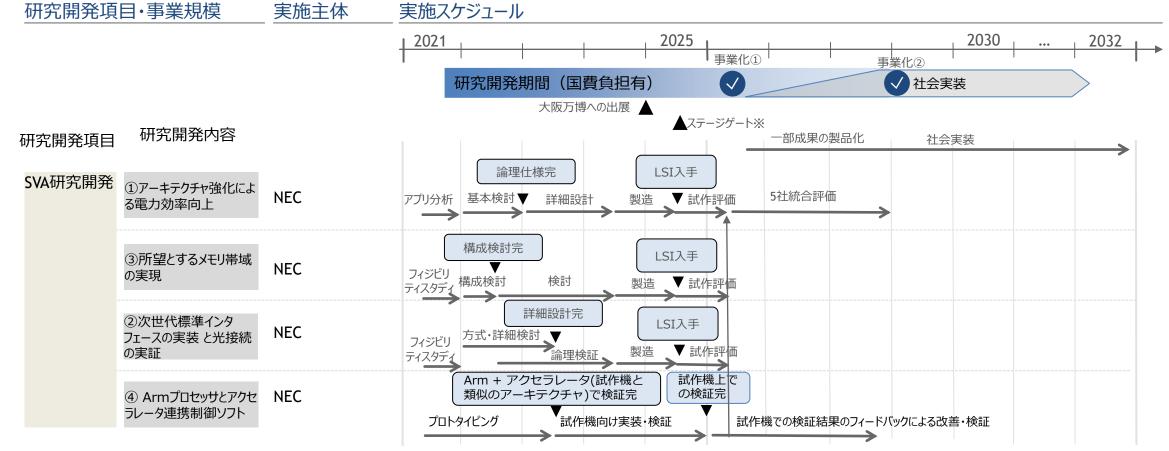

# 2.2 省電力アクセラレータ開発/(3) 実施スケジュール

# 複数の研究開発を効率的に連携させるためのスケジュールを計画

### 大阪万博

- ハードウェアエミュレータを使ったアクセラレータの動作デモ(画面表示等)

- アプリ (一部のカーネル) による性能・電力の動作シミュレーション結果、机上計算による電力性能を算出して、目標とするの電力性能の達成をポスターor画面で展示

- 一般のArmサーバと現行アクセラレータ製品を使い、Arm連携のソフトウェア利用環境を展示

## ステージゲート

◆ 大阪万博の展示内容をベースに、ハードウェアエミュレータを 使った動作デモと机上計算等による電力性能の精度を向 上させた検証結果の提示

## 2.2 省電力アクセラレータ開発/(4)研究開発体制

# 各主体の特長を生かせる研究開発実施体制と役割分担を構築

### 実施体制図

### 各主体の役割

•研究開発内容②-2省電力アクセラレータ開発は日本電気(株)が担当する

### 研究開発における連携方法(共同実施者間の連携)

- ・共同実施者で開発状況や課題を定期的に共有し、研究計画・目標の見直しなどの 連携を行う

- これらの連携により、ステージゲート、社会実装に向けて互いに連携し、KPI、及び、 アウトプットの目標達成を目指す

### 共同実施者以外の本プロジェクトにおける他実施者等との連携

- ②-3不揮発メモリ開発は本共同実施に含まれないが、不揮発メモリ開発の実施者とも定期的ミーテイングなどで連携を行う

- 次世代グリーンデータセンター用デバイス・システムに関する協議会を設置し、外部機関と連携を行う

## 2.2 省電力アクセラレータ開発/(5)技術的優位性

# 国際的な競争の中においても技術等における優位性を保有

#### 研究開発項目 研究開発内容 活用可能な技術等 競合他社に対する優位性・リスク 高性能ベクトル技術・広帯域ベクトルキャッシュ技術 アーキテクチャ ベクトル処理・ベクトルキャッシュ技術 省電力アクセラレータ は自社製品の経験よりNEC優位。但し、リスクとして 強化による電 (スケーラブル・ AI処理に適用可能なマトリクス演算技術 ベクトル技術は他社も導入しつつある 力効率向上 ベクトル・ 命令発行制御技術による省電力化 リスクとしてマトリクス演算技術に関してはフォロワーで アクセラレータ) あり、充分な検討・評価が必要である • ベクトル処理における独自技術は自社製品の実績 を活用する 所望とするメモリ ベクトルマルチコアの複数メモリアクセスにおける 現行当社製品で培ったメモリ帯域を確保する 技術からのシームレスな展開 帯域の実現 ネットワークオンチップの制御技術 HBMとプロセッサの混在させるチップレット技術 シリコンインターポーザーを介したHBM制御技術 の対応経験を活用する リスクとして規格への準拠、相互接続性がある 現行製品でのPCIe標準インタフェースと接続する 次世代標準イ 広帯域・低レイテンシ・低消費電力ネットワー ため設計・検証技術 ンタフェースの実 クオンチップ設計技術を保有する 装 Armプロセッサ • 汎用OS(posix互換)を期待するプログラムを、 特許技術による実現 •システムコール アクセラレータ上で動作させる技術 とアクセラレータ メモリマップドファイル 連携制御ソフト コンパイラおよび計算ライブラリによるベクトルアーキ •メモリ初期化 テクチャ向け最適化技術 • Stream, Hemeno等のベンチマークで他社より高い 性能を実現

# 3. イノベーション推進体制

(経営のコミットメントを示すマネジメントシート)

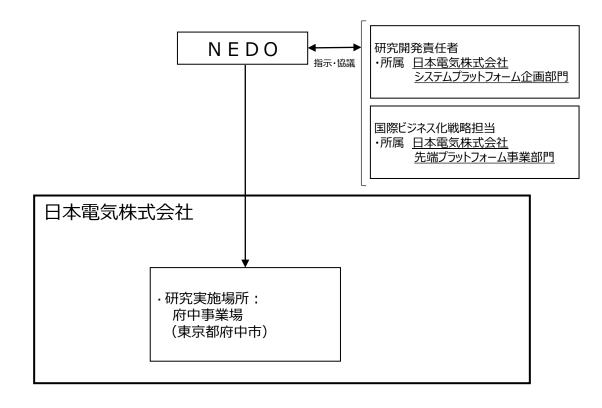

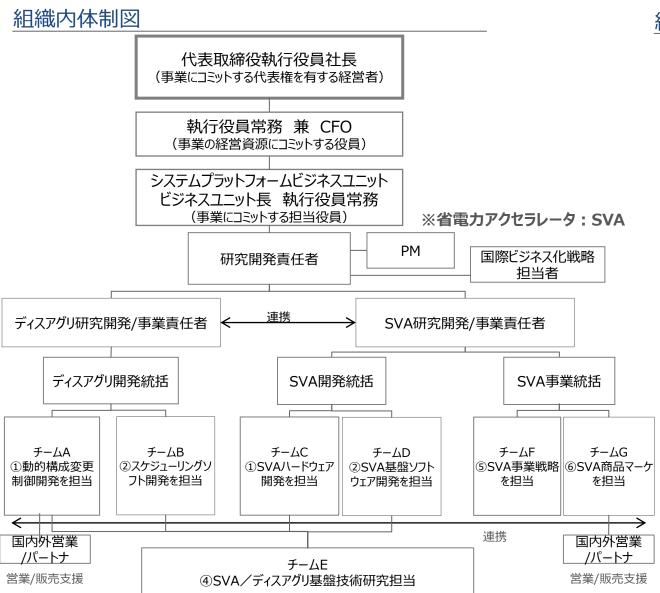

# 3. イノベーション推進体制/(1)組織内の事業推進体制

# 経営者のコミットメントの下、専門部署に複数チームを設置

### 組織内の役割分担

#### 研究開発責任者と担当部署

- 研究開発責任者

- 研究開発を統括

- 国際ビジネス化戦略担当者

- 拡販戦略を担当

- 担当チーム

- チームA: ①動的構成変更制御開発を担当

- チームB:②スケジューリングソフト開発を担当

- チームC: ① SVA ハードウェア (LSI、システム) 開発を担当

- チームD: ②SVA基盤ソフト開発を担当

- チームE:④SVA/ディスアグリ基盤技術研究を担当

- チームF: ⑤SVA 事業戦略を担当

- チームG: ⑥SVA 商品マーケ/拡販戦略を担当

#### 部門間の連携方法

- 協議会会合への必要チームリーダの出席

- 経営層への月次の定例報告等の中で進捗報告

- 社内SVA-ディスアグリ合同会議(週次~月次で状況により頻度は見直し)により連携

- 研究開発/事業責任者~各チームリーダまで出席の週次会議および報告により連携

- 各チーム内での週次定例ミーティングでのチームメンバへの連携事項周知と徹底図る

# 3. イノベーション推進体制/(2)マネジメントチェック項目① 経営者等の事業への関与

# 経営者等による事業への関与の方針

### 経営者等による具体的な施策・活動方針

- 経営者のリーダーシップ

- 「未来の共感を創る」というコーポレートビジョンの下、中長期の環境目標策定し、環境負荷等の継続的な低減と事業を通じた貢献の拡大に取組むことを社内外に発信

- 中期計画を毎年度更新する中で、社長、CFOの経営確認を実施し、事業 継続の有無を判断している

- 事業のモニタリング・管理

- 事業執行会議での報告、また中期計画の毎年の更新で経営層が確認。

- 月次の事業推進会議、および事業責任部門、特定注力事業の個別月例 報告において、事業/開発進捗をトレースしている

- 開発投資開始など節目での承認タイミングなどで方針確認修正など指示を 実施

- 事業責任部門にて事業単位ごとにビジネスプランを実現するKPIを設定。計画部門にて計数を客観的に評価するとともに進捗をモニタリングしている

### 経営者等の評価・報酬への反映

• 執行役員を含めた全社員が事業戦略/事業計画と連動した業績目標を 設定し、達成度に応じた評価を実施し、賞与において業績連動となっている

### 事業の継続性確保の取組

- 事業責任部門/事業単位ごとに5年の中期計画を作成。毎年の見直しは行うもののその計画作成にはビジネスユニット全体で取組んでおり、事業の継続性は確保されている

- この中期計画はコーポレートビジョンや中期的環境目標踏まえた全社方針を基に策定しており、担当役員レベルの他BUからの異動の場合にもその基本方針や理念の継承性は担保できている

- 一方、社会価値/技術の変化に応じ毎年の見直しを行うことで、価値/技術の変化にも柔軟に追従し事業性を確保可能なプロセスとしている

# 3. イノベーション推進体制/(3) マネジメントチェック項目② 経営戦略における事業の位置づけ

# 経営戦略の中核において事業を位置づけ、広く情報発信

### 取締役会等での議論

- 「未来の共感を創る」というコーポレートビジョンの下、中長期の環境目標策定し、環境負荷等の継続的な低減と事業を通じた貢献の拡大に取り組んでいる。具体的には、調達/製品としての環境負荷低減はもちろん、"地球と共生する"NECの環境ソリューション"としてDXで環境課題の解決するソリューションの提供を全社レベルで展開している

- 本研究の取り組みをグリーンITを推進する技術として社内外に発信しており、 全社~ビジネスユニットレベルで一貫して環境負荷軽減に取り組んでいる

- 事業戦略・事業計画の決議・変更

- 中期計画を毎年10-11月に見直し、社会環境/進捗状況踏まえた、 人員リソースの妥当性も確認する

- 開発プロセスにおいて計画/企画段階、設計完了段階などの節目ポイントにおいて次のステップに進むかどうかのジャッジをし、開発を担保する

- 決議事項と研究開発計画の関係

- 本研究開発を中期計画の見直し時に中核事項の一つとして盛り込んだ計画を決議することになるため、不可欠な高優先度の開発と位置付けて進めることとなる

### ステークホルダーに対する公表・説明

- 情報開示の方法

- 全社のIR報告などの際にも環境負荷低減活動の一部として、本活動の成果も含む形で公開される

- 製品として発表する際には本活動の成果であることを付記するとともに社会的価値や重要性との寄与を紹介する予定であり、その後も拡販/訴求活動のなかでそうした価値を提案してゆく

- ステークホルダーへの説明

- 製品エコシステムを作るパートナー企業に対して、注力技術領域とその 技術革新がもたらす社会的価値を説明。本開発の意義を意味づけることで開発への協力をとりつけ推進してゆく

- 本研究活動を各種アナリストとのブリーフィングの際にも説明してゆく

- 製品展開に効果的な開発節目でプレス発表を実施する

## 3. イノベーション推進体制/(4)マネジメントチェック項目③事業推進体制の確保

# 機動的に経営資源を投入し、着実に社会実装まで繋げられる組織体制を整備

### 経営資源の投入方針

- 実施体制の柔軟性の確保

- 経営資源の点検を事業執行会議、中期計画の見直し時に実施

- 各統括からの提言や事業責任部門の長の判断でリソースの追加を決 定する体制を構築

- 人材・設備・資金の投入方針

- ハードウェア、ソフトウェアの研究開発にあたる人材は、既存の製品開発技術者に加えて、若手・新卒技術者を育成しつつ、研究開発に必要な人員を適宜確保する。

- ハードウェア、ソフトウェア設計・評価向けに、社内設備を流用しつつ、本研究開発に固有の設備は国費で購入予定。

- 中期計画をベースに一年毎にリソース配置の妥当性確認と最適化を 行い人的資源・資金投入を継続する

### 専門部署の設置

- 専門部署の設置

- 既存製品の後継製品として位置づけ、事業責任者のもと専門部署で研究開発を行ってゆくことで、事業化に直結し事業社会環境にも即応する意思決定権を持った組織として進める

- 若手人材の育成

- 該当事業の継続/拡大戦略としての研究開発活動であり、該当事業の 持続的な発展のためベテランのノウハウ/技術を継承し若手人材の育成 を今後とも継続してゆく

# 4. その他

# 4. その他/(1) 想定されるリスク要因と対処方針

# リスクに対して十分な対策を講じるが、需要減や目標達成が不可能等の事態に陥った場合には 事業中止も検討

### 研究開発(技術)におけるリスクと対応

- 想定する半導体テクノロジ遅延によるリスク

- → 先端半導体Fab(\*1)の技術動向・稼働状況をウォッチして、生産可能時期を見極める

- 接続インターフェース規格化の遅延、機能不足のリスク

→ PCI sig(\*2)および、次世代標準インターフェース

(CXL(\*3)規格等)の会員として、規格化動向と内容を 随時確認する

- 想定するAI技術の行き詰まりによるリスク

- → 社内で保有するAI技術の動向やアカデミア含めた社外の技術動向をウォッチして活用を判断する

- ディスアグリゲーションのハードウェア技術の進展の遅延、 機能不足のリスク

- → PCI sigおよび、次世代標準インターフェースの会員 として、規格化動向と内容を随時確認する。海外のベン ダーのロードマップを確認する

### 社会実装(経済社会)におけるリスクと対応

- 経済活動の変化による次世代データセンターの需要停滞や要件変化によるリスク

- → 今後、需要増大が予想されている次世代データセンターの動向、要件(特に機能・電力・性能)等を適宜を確認する

- 実社会に適合したAIモデルの構築ができないリスク

→ アーリーアダプタや自社DCでの適用で経験を積み、AIモデルの構築に努める

### その他(自然災害等)のリスクと対応

- サプライチェーン破綻によるリスク

- → LSI製造拠点の稼働状況の確認、調達部材のマルチベンダー化を実施

- COVID-19などの蔓延による事業継続リスク

→ リモートワークの仕組みを継続強化すると共に社

内風土の継続した変革を遂行

● 事業中止の判断基準: 省電力アクセラレータの電力効率等の目標達成が困難と判断された場合

<sup>(\*2)</sup> PCI sig: 汎用の拡張インターフェス規格であるPCI(Peripheral Component Interconnect)の策定および管理をおこなっている組織 (\*3) CXL: Compute Express Link。次世代のCPU-デバイス、CPU-メモリ間を接続するためのインターフェース規格